## ECC DRAM

#### IME5132SDBE(T/B) 512Mbit SDRAM <u>with integrated ECC error correction</u> 4 BANKS X 4Mbit X 32

|                                                 | 6       | 75      |

|-------------------------------------------------|---------|---------|

| System Frequency ( $f_{CK3}$ ) CAS Latency = 3  | 166 MHz | 133 MHz |

| System Frequency ( $f_{CK2}$ ) CAS Latency = 2  | 100 MHz | 100 MHz |

| Clock Cycle Time ( $t_{CK3}$ ) CAS Latency = 3  | 6 ns    | 7.5 ns  |

| Clock Cycle Time ( $t_{CK2}$ ) CAS Latency = 2  | 10 ns   | 10 ns   |

| Clock Access Time ( $t_{AC3}$ ) CAS Latency = 3 | 5.4 ns  | 5.4 ns  |

| Clock Access Time ( $t_{AC2}$ ) CAS Latency = 2 | 6 ns    | 6 ns    |

#### Features

- 4 banks x 4Mbit x 32 organization

- High speed data transfer rates up to 166 MHz

- Full Synchronous Dynamic RAM, with all signals referenced to clock rising edge

- Single Pulsed RAS Interface

- Data Mask for Read/Write Control

- Four Banks controlled by BA0 & BA1

- Programmable CAS Latency: 2, 3

- Programmable Wrap Sequence: Sequential or Interleave

- Programmable Burst Length:

- 1, 2, 4, 8 and full page for Sequential Type

- 1, 2, 4, 8 for Interleave Type

- Multiple Burst Read with Single Write Operation

- Automatic and Controlled Precharge Command

- Random Column Address every CLK (1-N Rule)

- Power Down Mode

- Auto Refresh and Self Refresh

- Refresh Interval: 4096 cycles/64ms

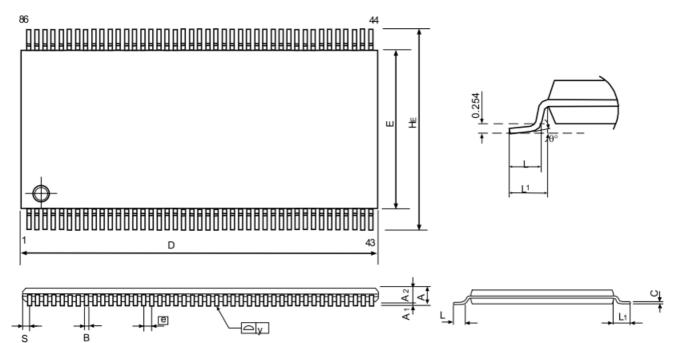

- Available in 90 Ball FBGA and 86 Pin TSOP II

- LVTTL Interface

- Single 3.3 V ± 0.3 V Power Supply

- Refresh cycles:

- Average refresh period Commercial: 64ms at  $0^{\circ}C \le Tambient \le +70^{\circ}C$ Industrial: 64ms at  $-40^{\circ}C \le Tambient \le +85^{\circ}C$ High Temperature: 64ms at  $-40^{\circ}C \le Tambient \le +105^{\circ}C$ X-temp of Extreme Temperature: 64ms at  $-40^{\circ}C \le Tambient \le +125^{\circ}C$ Y-temp of Extreme Temperature: 64ms at Tcase  $\le +105^{\circ}C$ 32ms at Tcase  $> +105^{\circ}C$

- \* Min/Max temperature value depends on the temperature range of the specific device

- Operating temperature range

- Commercial Tambient = 0°C to +70°C

- Industrial Tambient = -40°C to +85°C

- High Temperature

- Tambient = -40°C to +105°C, Tcase(max) = +115°C

- X-temp and Y-temp of Extreme Temperature

- Tambient =  $-40^{\circ}$ C to  $+125^{\circ}$ C, Tcase(max) =  $+135^{\circ}$ C

\* Tcase and Tambient must not exceed the maximum operating temperature

| Option                                               | Marking         |

|------------------------------------------------------|-----------------|

| Configuration                                        |                 |

| - 16Mx32 (4 banks x 4Mbit x 32)                      | 5132            |

| Package                                              |                 |

| - 86-pin TSOP                                        | Т               |

| - 90-ball FBGA (8mm x13mm)                           | В               |

| Leaded/Lead-free                                     |                 |

| - Leaded                                             | <blank></blank> |

| - Lead-free/RoHS                                     | G               |

| Speed/Cycle Time                                     |                 |

| - 6 ns @ CL3 (PC166)                                 | -6              |

| - 7.5 ns @ CL3 (PC133)                               | -75             |

| Temperature                                          |                 |

| - Commercial 0°C to +70°C Tambient                   | <blank></blank> |

| - Industrial -40°C to +85°C Tambient                 | I               |

| - High temperature -40°C to +105°C Tambient          | н               |

| (Tcase max +115°C)                                   | П               |

| - Extreme temperature -40°C to +125°C                | X, Y            |

| Tambient (Tcase max +135°C)                          | Λ, Ι            |

| Automotive Grade                                     |                 |

| - Non-Automotive                                     | <blank></blank> |

| - Automotive AEC-Q100                                | А               |

| * Possible combinations: IA = AEC-Q100 Grade 3, HA = | = AEC-Q100      |

|                                                      |                 |

Grade 2, XA/YA = AEC-Q100 Grade 1

#### Example Part Number: IME5132SDBETG-6IA

#### Description

The IME5132SDBE(T/B) is a four bank Synchronous DRAM organized as 4 banks x 4Mbit x 32. The IME2532SDBE(T/B) achieves high speed data transfer rates up to 166 MHz by employing a chip architecture that prefetches multiple bits and then synchronizes the output data to a system clock.

All of the control, address, data input and output circuits are synchronized with the positive edge of an externally supplied clock.

Operating the four memory banks in an interleaved fashion allows random access operation to occur at higher rate than is possible with standard DRAMs. A sequential and gapless data rate of up to 166 MHz is possible depending on burst length,  $\overline{CAS}$  latency and speed grade of the device.

## Special Features (ECC – Functionality)

- Embedded error correction code (ECC) functionality corrects single bit errors within each 64 bit memory-word.

- The error correction is performed automatically inside the ECC DRAM device.

- Parity data is generated by an internal ECC logic and then stored in additional, dedicated memory space

- Fully compatible to JEDEC standard DRAM operation and timings

- JEDEC compliant FBGA package (drop in replacement)

#### ECC – Functionality / Challenges and Achievements

During the production test, the ECC DRAMs are verified to pass extensive burn-in, core-function and speed tests throughout the complete memory array, including the memory-space for the parity-data. Only when every single memory cell has passed these tests, the ECC function is switched on by hardware and the products get shipped. With the ECC function activated, customers will have unparalleled functionality and quality.

#### Embedded ECC functionality

Intelligent Memory ECC DRAMs are JEDEC compliant components with integrated error-correction. The internal logic automatically detects and corrects single-bit-errors "on the fly" without any delays or additional latencies compared to conventional DRAM components. ECC DRAMs have additional memory-space to store the ECC-check-bits. Internally, the ECC DRAM works with a 72 bit wide buffer. When writing to the DRAM, an additional 8 ECC check-bits are being generated per each 64 bit data-word. Upon a Read-command, the whole 64+8 bit word is transferred to the buffer and automatically corrected by an ECC Hamming Code (72, 64). The corrected data is then applied to the DQ lines of the ECC DRAM in bit-widths of 4, 8, 16 or 32 bit, depending on the organization of the device.

The ECC algorithm is able to detect and correct one bit-error per 64+8 bit data-word. A 1 Gigabit ECC DRAM component has 16,777,216 data-words of 64 Bits. In each of these data-words, one single-bit error could be corrected, resulting in approximately 16 million times higher reliability of ECC DRAM compared to a conventional DRAM with similar capacity.

Note: If Burst Length x DRAM-I/O-width < 64 bit during a Write-command, the ECC-functionality is limited. Please contact Intelligent Memory for further details.

#### Comparison to conventional ECC implementation

ECC error correction is very common on high end industrial applications and servers. It normally requires an ECC-capable memory-controller which has an extra-wide data-bus with for example 72 bits (64 data-bits + 8 check-bits). The memory controller generates the required additional check-bits for the data and writes the extra wide data-word to the memory. Upon a Read-command, the memory controller will verify the data-integrity of the data-word + check-bits and performs the correction algorithm. Performing this algorithm affects the systems performance. In addition to the requirement for an ECCcapable memory controller, the conventional way of ECC correction requires multiple DRAMs to be accessed in parallel to achieve the extra-wide bitwidth. On Server-memory-modules, for example, 18 DRAM-components with 4 data-lines each are put in parallel to reach the total 72 bit extra-wide databus.

With IM ECC DRAM, the check-bit-generation, verification and correction is performed inside the memory device. Every single ECC DRAM performs the error correction by itself, thus it does not require ECC-capable processors/controllers nor any wide data-bus between the controller and the DRAM. Because the ECC DRAM components are JEDEC compliant, they are drop-in replacements to conventional DRAM-memory. Any existing application that is currently built with conventional DRAM can be equipped with error-correction functionality. Note that, if a standard 64 bit memory-module is built using ECC DRAMs, the depth of error-correction is deeper than on 72 bit ECC memory module as each DRAM component on the module performs its own ECC correction-algorithm.

## Why is ECC error correction important?

DATASHEFT

Numerous analyzes and field-studies have proven DRAM single-bit errors to be the root cause of system-malfunctions or data-corruptions.

According to the field-study by the University Of Toronto called "DRAM Errors In The Wild – A Large-Scale field study", 25000 to 70000 ECC correctable single-bit errors occur per Megabit of DRAM within 1 billion hours of operation.

While not every single bit error causes a system crash, the application-software may become unstable or important data can be altered and the wrong data can pass through to external media, resulting in unrecoverable data-errors.

While all DRAMs are factory-tested by long burn-in-testing and effective functional and speed testing with different patterns and voltage variations, singlebit errors are technically not avoidable.

The effects are typically transient and difficult-to-repeat single data-bit flips. Many of these single-bit errors appear only under heavy stress or longer time of use of the DRAM, resulting as random system malfunctions or data-corruptions of the application. After a reset, the systems work again until the next occurrence of a single bit error reappears. It is difficult to prove a defect, as it is only a random effect which shows up in different ways at unknown times.

ECC corrects the output, but not the content of the Memory Array. For maximum stability we recommend to do periodical "scrubbing" (read and overwrite)

#### Possible root-causes for single-bit errors

DRAM cells consist of capacitors holding an electric charge which defines if the memory-cell contains a logical 0 or a 1. These capacitor-cells are switched by transistors.

With the trend to smaller process technologies, higher speeds and lower supply-voltages, DRAM memory cells become more sensitive to noise on the signals, electromagnetic fields, cosmic rays or particle radiation. Also power peaks and variations in the signal-timing can cause single-bit errors.

Furthermore, depending on the age and intensity of use of those DRAM components, memory-cells suffer from various degrees of degradation. The isolation of the capacitors gets reduced and leakage increases, leading to lower data-retention-times of some cells. As data-retention times approach the refresh-times, data-bit tend to sometimes show up an incorrect binary value. The effects often appear only with certain data-patterns, at specific temperatures or at high data-traffic to the DRAM. The cell gets "weak", but the errors in the cell are not easily repeatable as they are not permanent.

There is no way to improve the DRAM technology itself, except by going back to larger processes, lower speeds and higher voltages. Pre-Testing the DRAMs longer, with more stress and wider guardbands, or even with automotive certified screening-processes does not fully protect from the risk of single-bit errors.

The only practical way to avoid single-bit errors is to use error correction algorithms such as ECC.

INTELLIGENT

## UNLIMITED INGENUIT

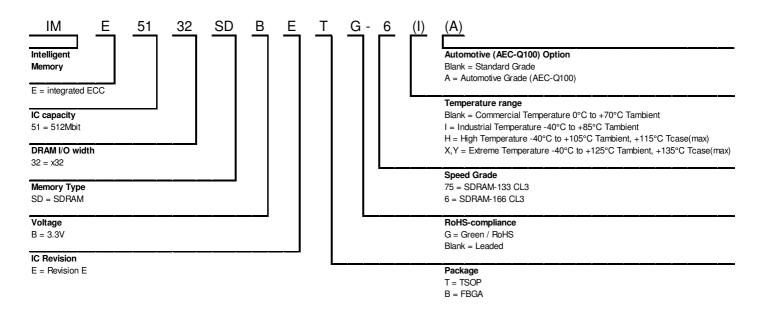

## Part Number Information

DATASHEET

| Description | Pkg. | Pin Count |

|-------------|------|-----------|

| TSOP-II     | Т    | 86        |

#### 86 Pin Plastic TSOP-II x32 Pin Configurations Top View

| ST2222 - 14 |    |           |

|-------------|----|-----------|

| VDD C       | 10 | 86 🔲 VSS  |

|             | 2  | 85 DQ15   |

| VDDQ        | 3  | 84 VSSQ   |

| DQ1         | 4  | 83 DQ14   |

|             | 5  |           |

| DQ2         |    | 82 DQ13   |

| VSSQ 🗖      | 6  | 81 VDDQ   |

| DQ3         | 7  | 80 DQ12   |

| DQ4         | 8  | 79 DQ11   |

| VDDQ C      | 9  | 78 VSSQ   |

| DQ5         | 10 | 77 DQ10   |

| DQ6         | 11 | 76 009    |

| VSSQ C      | 12 | 75 VDDQ   |

| D07         | 13 | 74 DQ8    |

| NC          | 14 | 73 INC    |

|             |    |           |

|             | 15 | 72 VSS    |

|             | 16 | 71 DQM1   |

| WE#         | 17 | 70 🔲 NC   |

| CAS#        | 18 | 69 🔲 NC   |

| RAS#        | 19 | 68 🔲 CLK  |

| CS#         | 20 | 67 🔲 CKE  |

| A11         | 21 | 66 🗔 A9   |

| BA0         | 22 | 65 🗔 A8   |

| BA1         | 23 | 64 🗖 A7   |

| A10/AP      | 24 | 63 A6     |

| A0          | 25 | 62 A5     |

| A1          | 26 | 61 A4     |

|             | 27 |           |

|             |    |           |

| DQM2        | 28 | 59 DQM3   |

| VDD C       | 29 | 58 🔲 VSS  |

| NC C        | 30 | 57 🔲 NC   |

| DQ16        | 31 | 56 🔲 DQ31 |

| VSSQ        | 32 | 55 D VDDQ |

| DQ17        | 33 | 54 🗔 DQ30 |

| DQ18        | 34 | 53 DQ29   |

|             | 35 | 52 VSSQ   |

| DQ19        | 36 | 51 DQ28   |

| DQ20        | 37 | 50 DQ27   |

| VSSQ        | 38 |           |

|             |    |           |

| DQ21        | 39 | 48 DQ26   |

| DQ22        | 40 | 47 DQ25   |

| VDDQ        | 41 | 46 VSSQ   |

| DQ23        | 42 | 45 DQ24   |

| VDD 🖂       | 43 | 44 🗔 VSS  |

| 2750.6W (d  |    |           |

## Pin Names

| CLK              | Clock Input                        |

|------------------|------------------------------------|

| CKE              | Clock Enable                       |

| CS               | Chip Select                        |

| RAS              | Row Address Strobe                 |

| CAS              | Column Address Strobe              |

| WE               | Write Enable                       |

| A0-A12           | Address Inputs                     |

| BA0, BA1         | Bank Select                        |

| DQ0-DQ31         | Data Input/Output                  |

| DQM0-DQM3        | Data Mask                          |

| V <sub>DD</sub>  | Power (3.3V ± 0.3 V)               |

| V <sub>SS</sub>  | Ground                             |

| V <sub>DDQ</sub> | Power for I/O's $(3.3V \pm 0.3 V)$ |

| V <sub>SSQ</sub> | Ground for I/O's                   |

| NC               | Not connected                      |

## **Pin Configurations**

DATASHEET

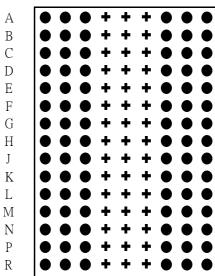

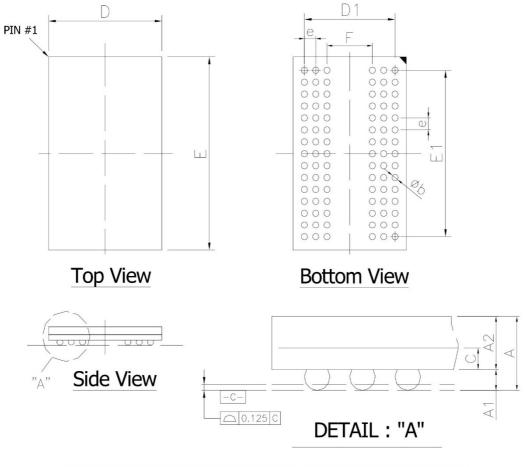

## 90-ball FBGA (x32 configuration)

|   | 1                | 2                | 3                | 4 | 5 | 6 | 7               |

|---|------------------|------------------|------------------|---|---|---|-----------------|

| А | DQ26             | DQ24             | V <sub>SS</sub>  |   |   |   | V <sub>DE</sub> |

| В | DQ28             | V <sub>DDQ</sub> | V <sub>SSQ</sub> |   |   |   | V <sub>DD</sub> |

| С | V <sub>SSQ</sub> | DQ27             | DQ25             |   |   |   | DQ2             |

| D | V <sub>SSQ</sub> | DQ29             | DQ30             |   |   |   | DQ1             |

| Е | V <sub>DDQ</sub> | DQ31             | NC               |   |   |   | NC              |

| F | V <sub>SS</sub>  | DQM3             | A3               |   |   |   | A2              |

| G | A4               | A5               | A6               |   |   |   | A10             |

| Н | A7               | A8               | A12              |   |   |   | NC              |

| J | CLK              | CKE              | A9               |   |   |   | BA              |

| к | DQM1             | NC               | NC               |   |   |   | CAS             |

| L | $V_{\text{DDQ}}$ | DQ8              | V <sub>SS</sub>  |   |   |   | VDD             |

| М | V <sub>SSQ</sub> | DQ10             | DQ9              |   |   |   | DQ              |

| Ν | V <sub>SSQ</sub> | DQ12             | DQ14             |   |   |   | DQ              |

| Р | DQ11             | $V_{\text{DDQ}}$ | $V_{\text{SSQ}}$ |   |   |   | $V_{DD}$        |

| R | DQ13             | DQ15             | $V_{SS}$         |   |   |   | VDD             |

|   |                  |                  |                  |   |   |   |                 |

Ball Location (x32)

- Populated ball

- Ball not populated

Top view

(See the balls through the package)

| 7                | 8                | 9                |   |

|------------------|------------------|------------------|---|

| V <sub>DD</sub>  | DQ23             | DQ21             | А |

| V <sub>DDQ</sub> | V <sub>SSQ</sub> | DQ19             | В |

| DQ22             | DQ20             | V <sub>DDQ</sub> | С |

| DQ17             | DQ18             | $V_{\text{DDQ}}$ | D |

| NC               | DQ16             | $V_{SSQ}$        | Е |

| A2               | DQM2             | V <sub>DD</sub>  | F |

| A10              | A0               | A1               | G |

| NC               | BA1              | A11              | Н |

| BA0              | CS               | RAS              | J |

| CAS              | WE               | DQM0             | К |

| V <sub>DD</sub>  | DQ7              | $V_{SSQ}$        | L |

| DQ6              | DQ5              | $V_{\text{DDQ}}$ | М |

| DQ1              | DQ3              | $V_{\text{DDQ}}$ | Ν |

| $V_{\text{DDQ}}$ | $V_{SSQ}$        | DQ4              | Р |

| $V_{\text{DD}}$  | DQ0              | DQ2              | R |

UNLIMITED INGENUITY

2 3 4 5 6 7 8 9

1

#### Capacitance\*

(at Tambient = 0°C to 25°C,  $V_{DD}$  =  $V_{DDQ}$  = 3.3 V ± 0.3 V)

| Parameter                                         | Symbol           | Min. | Max. | Unit |

|---------------------------------------------------|------------------|------|------|------|

| Input Capacitance: CLK                            | C <sub>CLK</sub> | 4.5  | 6    | pF   |

| Input Capacitance: All other input pins and balls | C <sub>IN</sub>  | 2.5  | 6    | pF   |

| Input/Output Capacitance:<br>DQ                   | C <sub>I/O</sub> | 4    | 6    | pF   |

\*Note: Capacitance is sampled and not 100% tested.

#### Absolute Maximum Ratings\*

| Operating temperature range:                                    |

|-----------------------------------------------------------------|

| Tambient: 0°C to +70°C for Commercial Temp.                     |

| Tambient: -40°C to +85°C for Industrial Temp.                   |

| Tambient: -40°C to +105°C, Tcase(max): +115°C for High Temp.    |

| Tambient: -40°C to +125°C, Tcase(max): +135°C for Extreme Temp. |

| Storage temperature range55°C to +150°C                         |

| Input/output voltage0.3V to (V_{DD} $\pm$ 0.3)V                 |

| Power supply voltage0.3V to 4.6V                                |

| Power dissipation1W                                             |

| Data out current (short circuit)50mA                            |

|                                                                 |

\*Note: Stresses above those listed under "Absolute Maximum Ratings\* may cause permanent damage of the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

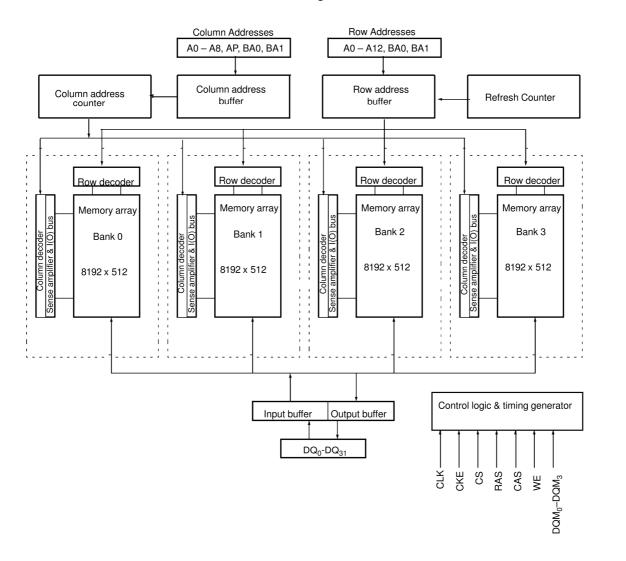

## Block Diagram

x32 Configuration

## Signal Pin Description

| Pin                                             | Туре            | Signal | Polarity         | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------------------------------------|-----------------|--------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK                                             | Input           | Pulse  | Positive<br>Edge | The system clock input. All of the SDRAM inputs are sampled on the rising edge of the clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| CKE                                             | Input           | Level  | Active High      | Activates the CLK signal when high and deactivates the CLK signal when low, thereby initiates either the Power Down mode or the Self Refresh mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| CS                                              | Input           | Pulse  | Active Low       | CS enables the command decoder when low and disables the command decoder when high.<br>When the command decoder is disabled, new commands are ignored but previous operations continue.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| $\overline{RAS}, \overline{CAS}, \overline{WE}$ | Input           | Pulse  | Active Low       | When sampled at the positive rising edge of the clock, $\overline{CAS}$ , $\overline{RAS}$ , and $\overline{WE}$ define the command to be executed by the SDRAM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| A0 - A12                                        | Input           | Level  | -                | <ul> <li>During a Bank Activate command cycle, A0-A12 defines the row address (RA0-RA12) when sampled at the rising clock edge.</li> <li>During a Read or Write command cycle, A0-An defines the column address (CA0-CAn) when sampled at the rising clock edge.CAn depends from the SDRAM organization:</li> <li>16M x 32 SDRAM CA0–CA8.</li> <li>In addition to the column address, A10(=AP) is used to invoke autoprecharge operation at the end of the burst read or write cycle. If A10 is high, autoprecharge is selected and BA0, BA1 defines the bank to be precharged. If A10 is low, autoprecharge is disabled. During a Precharge command cycle, A10(=AP) is used in conjunction with BA0 and BA1 to control which bank(s) to precharge. If A10 is high, all four banks will BA0 and BA1 are used to define which bank to precharge.</li> </ul> |

| BA0, BA1                                        | Input           | Level  | -                | Selects which bank is to be active.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| DQx                                             | Input<br>Output | Level  | -                | Data Input/Output pins operate in the same manner as on conventional DRAMs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| DQM0 –<br>DQM3                                  | Input           | Pulse  | Active High      | The Data Input/Output mask places the DQ buffers in a high impedance state when sampled high.<br>In Read mode, DQM has a latency of two clock cycles and controls the output buffers like an<br>output enable. In Write mode, DQM has a latency of zero and operates as a word mask by<br>allowing input data to be written if it is low but blocks the write operation if DQM is high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| $V_{DD}, V_{SS}$                                | Supply          | -      | -                | Power and ground for the input buffers and the core logic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| V <sub>DDQ</sub> , V <sub>SSQ</sub>             | Supply          | -      | -                | Isolated power supply and ground for the output buffers to provide improved noise immunity.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

## **Operation Definition**

All of SDRAM operations are defined by states of control signals  $\overline{CS}$ ,  $\overline{RAS}$ ,  $\overline{CAS}$ ,  $\overline{WE}$  and DQM at the positive edge of the clock. The following list shows the truth table for the operation commands.

| Operation                 | Device<br>State     | CKE<br>n-1 | CKE | CS | RAS | CAS | WE | DQM | A0-9,<br>A11,<br>A12 | A10 | BS0,<br>BS1 |  |

|---------------------------|---------------------|------------|-----|----|-----|-----|----|-----|----------------------|-----|-------------|--|

| Row Activate              | Idle <sup>3</sup>   | н          | X   | L  | L   | Н   | н  | X   | V                    | V   | V           |  |

| Read                      | Active <sup>3</sup> | Н          | Х   | L  | Н   | L   | Н  | х   | V                    | L   | V           |  |

| Read w/ Autoprecharge     | Active <sup>3</sup> | Н          | Х   | L  | н   | L   | н  | Х   | V                    | Н   | V           |  |

| Write                     | Active <sup>3</sup> | Н          | Х   | L  | Н   | L   | L  | Х   | V                    | L   | V           |  |

| Write w/ Auto precharge   | Active <sup>3</sup> | Н          | Х   | L  | Н   | L   | L  | Х   | V                    | Н   | V           |  |

| Row Precharge             | Any                 | Н          | Х   | L  | L   | Н   | L  | Х   | Х                    | L   | V           |  |

| Precharge all             | Any                 | Н          | Х   | L  | L   | н   | L  | Х   | Х                    | Н   | Х           |  |

| Mode Register Set         | Idle                | Н          | Х   | L  | L   | L   | L  | Х   | V                    | V   | V           |  |

| No Operation              | Any                 | Н          | Х   | L  | н   | н   | Н  | Х   | х                    | Х   | х           |  |

| Device Deselect           | Any                 | Н          | Х   | н  | х   | х   | Х  | Х   | х                    | Х   | х           |  |

| Auto Refresh              | Idle                | Н          | н   | L  | L   | L   | н  | Х   | Х                    | Х   | Х           |  |

| Self Refresh Entry        | Idle                | Н          | L   | L  | L   | L   | н  | Х   | х                    | Х   | х           |  |

|                           | Idle                |            |     | н  | х   | х   | Х  | v   | ×                    | V   | V           |  |

| Self Refresh Exit         | (Self Refr.)        | L          | Н   | L  | н   | н   | Х  | X   | Х                    | Х   | Х           |  |

| Devuer Devue Entry        | Idle                |            |     | н  | Х   | Х   | Х  | v   | x                    | х   | v           |  |

| Power Down Entry          | Active <sup>4</sup> | Н          | L   | L  | н   | н   | Х  | X   | ~                    | X   | Х           |  |

|                           | Any                 |            |     | Н  | Х   | Х   | Х  |     |                      |     |             |  |

| Power Down Exit           | (Power<br>Down)     | L          | Н   | L  | н   | Н   | L  | Х   | Х                    | Х   | X           |  |

| Data Write/Output Enable  | Active              | Н          | Х   | Х  | Х   | Х   | Х  | L   | Х                    | Х   | Х           |  |

| Data Write/Output Disable | Active              | Н          | Х   | Х  | х   | х   | Х  | н   | х                    | Х   | х           |  |

Notes:

1. V = Valid, x = Don't Care, L = Low Level, H = High Level

2. CKEn signal is input level when commands are provided, CKEn-1 signal is input level one clock before the commands are provided.

3. These are state of bank designated by BS0, BS1 signals.

4. Power Down Mode can not entry in the burst cycle.

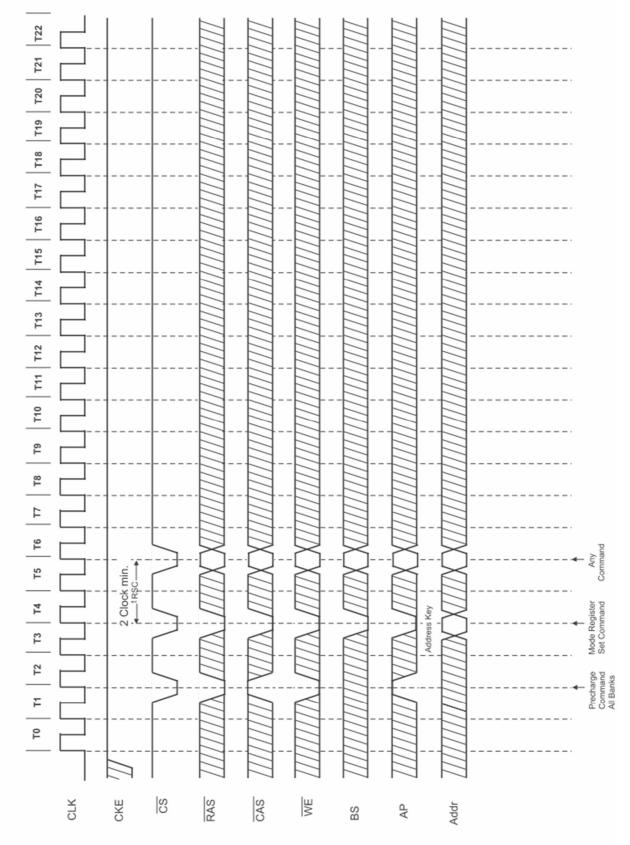

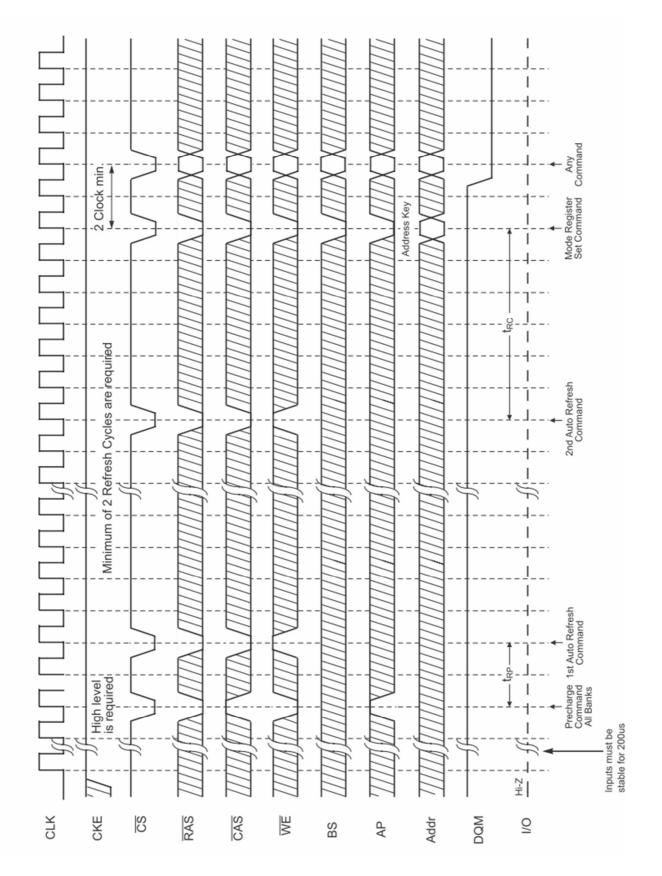

## Power On and Initialization

DATASHEFT

The default power on state of the mode register is supplier specific and may be undefined. The following power on and initialization sequence guarantees the device is preconditioned to each users specific needs. Like a conventional DRAM, the Synchronous DRAM must be powered up and initialized in a predefined manner. During power on, all  $V_{DD}$  and  $V_{DDQ}$  pins must be built up simultaneously to the specified voltage when the input signals are held in the "NOP" state. The power on voltage must not exceed  $V_{DD}$ +0.3 V on any of the input pins or  $V_{DD}$  supplies. The CLK signal must be started at the same time. After power on, an initial pause of 200 us is required followed by a precharge of both banks using the precharge command. To prevent data contention on the DQ bus during power on, it is required that the DQM and CKE pins be held high during the initial pause period. Once all banks have been precharged, the Mode Register Set Command must be issued to initialize the Mode Register. A minimum of two Auto Refresh cycles (CBR) are also required. These may be done before or after programming the Mode Register. Failure to follow these steps may lead to unpredictable start-up modes.

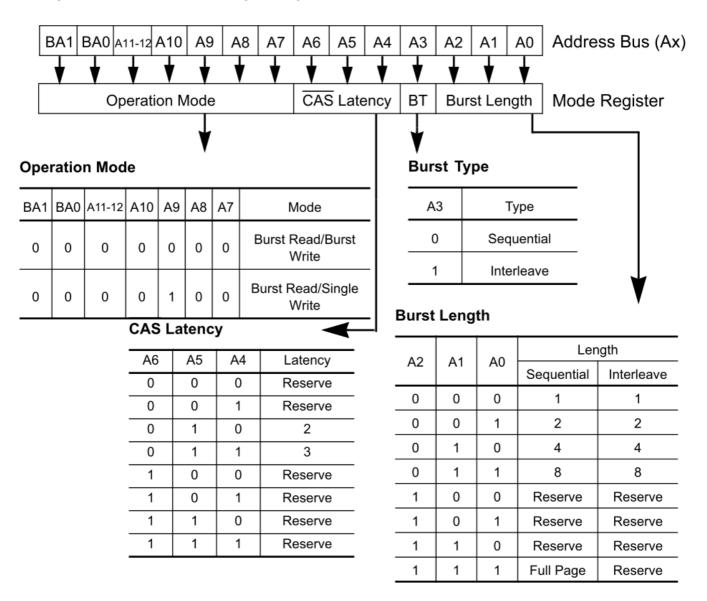

#### Programming the Mode Register

The Mode register designates the operation mode at the read or write cycle. This register is di- vided into 4 fields. A Burst Length Field to set the length of the burst, an Addressing Selection bit to program the column access sequence in a burst cy- cle (interleaved or sequential), a CAS Latency Field to set the access time at clock cycle and a Operation mode field to differentiate between normal op- eration (Burst read and burst Write) and a special Burst Read and Single Write mode. The mode set operation must be done before any activate com- mand after the initial power up. Any content of the mode register can be altered by re-executing the mode set command. All banks must be in precharged state and CKE must be high at least one clock before the mode set operation.

After the mode register is set, a Standby or NOP command is re- quired. Low signals of RAS, CAS, and WE at the positive edge of the clock activate the mode set op- eration. Address input data at this timing defines pa- rameters to be set as shown in the previous table.

## Read and Write Operation

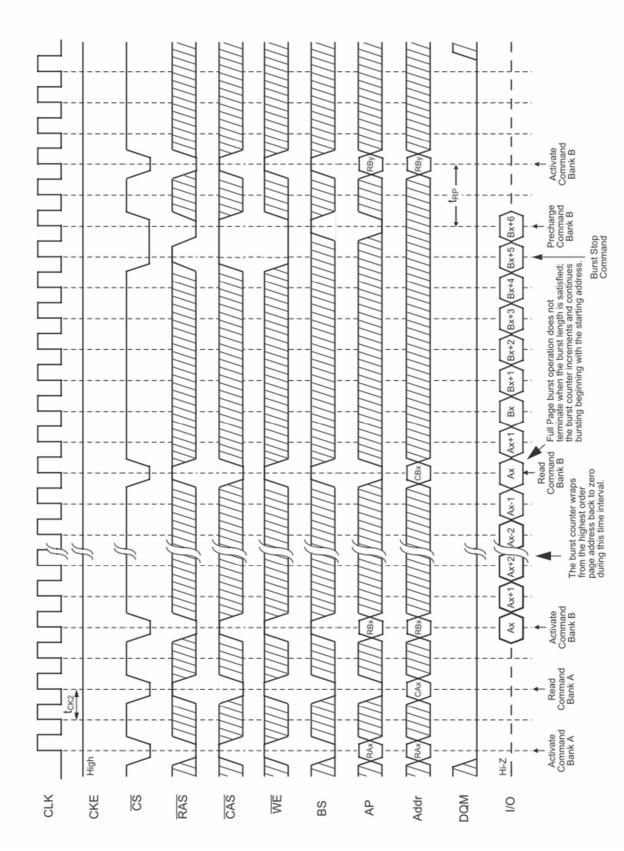

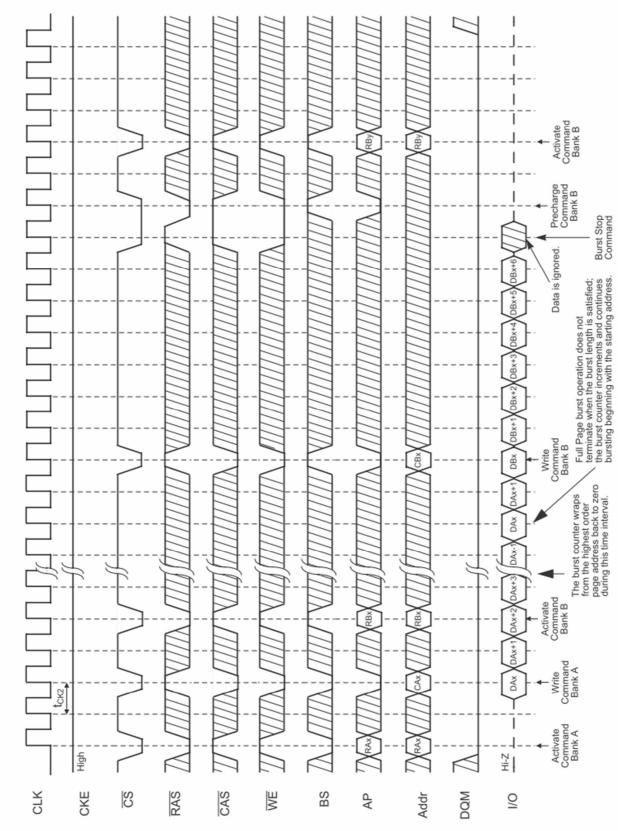

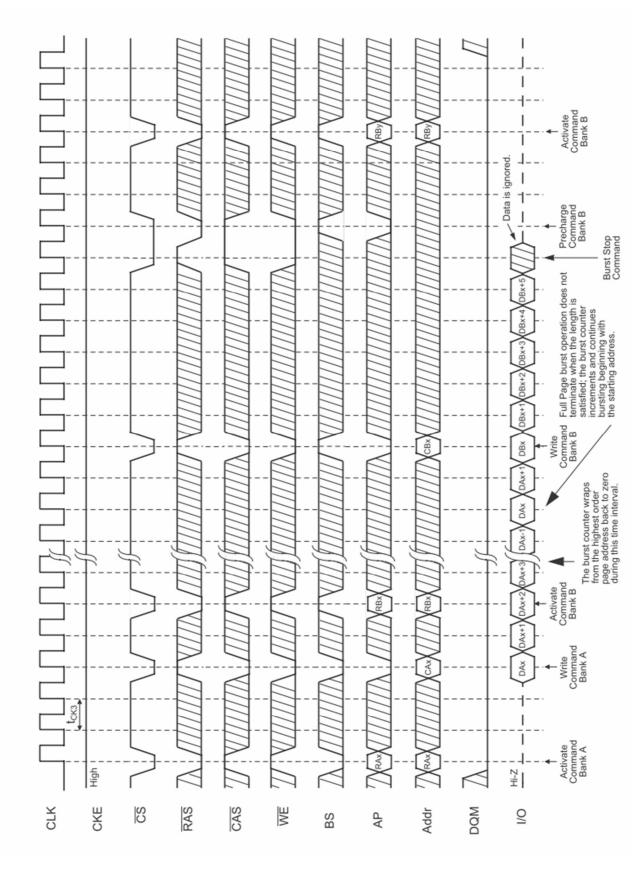

When  $\overline{RAS}$  is low and both  $\overline{CAS}$  and  $\overline{WE}$  are high at the positive edge of the clock, a  $\overline{RAS}$  cycle starts. According to address data, a word line of the selected bank is activated and all of sense amplifiers associated to the wordline are set. A  $\overline{CAS}$  cycle is triggered by setting  $\overline{RAS}$  high and  $\overline{CAS}$  low at a clock timing after a necessary delay,  $t_{RCD}$ , from the  $\overline{RAS}$  timing.  $\overline{WE}$  is used to define either a read ( $\overline{WE} = H$ ) or a write ( $\overline{WE} = L$ ) at this stage. SDRAM provides a wide variety of fast access modes. In a single  $\overline{CAS}$  cycle, serial data read or write operations are allowed at up to a 166 MHz data rate. The numbers of serial data bits are the burst length programmed at the mode set operation, i.e., one of 1, 2, 4, 8 and full page. Column addresses are segmented by the burst length and serial data accesses are done within this boundary. The first column address to be accessed is supplied at the  $\overline{CAS}$  timing and the subsequent addresses are generated automatically by the programmed burst length and its sequence. For example, in a burst length of 8 with interleave sequence, if the first ad- dress is '2', then the rest of the burst sequence is 3, 0, 1, 6, 7, 4, and 5.

Full page burst operation is only possible using sequential burst type. Full Page burst operation does not terminate once the burst length has been reached. (At the end of the page, it will wrap to the start address and continue.) In other words, unlike burst length of 2, 4, and 8, full page burst continues until it is terminated using another command.

INTELLIGENT

#### Address Input for Mode Set (Mode Register Operation)

Similar to the page mode of conventional DRAM's, burst read or write accesses on any column address are possible once the  $\overline{RAS}$  cycle latches the sense amplifiers. The maximum  $t_{RAS}$  or the refresh interval time limits the number of random column accesses. A new burst access can be done even before the previous burst ends. The interrupt operation at every clock cycles is supported. When the previous burst is interrupted, the remaining addresses are overridden by the new address with the full burst length. An interrupt which accompanies with an operation change from a read to a write is possible by exploiting DQM to avoid bus contention.

When two or more banks are activated sequentially, interleaved bank read or write operations are possible. With the programmed burst length, alternate access and precharge operations on two or more banks can realize fast serial data access modes among many different pages. Once two or more banks are activated, column to column interleave operation can be done between different pages.

#### Burst Length and Sequence

| Burst<br>Length | Starting Address<br>(A2 A1 A0) | Sequential Burst Addressing<br>(decimal) |            |   |       |      |   |   |   | In         | terle | eave | Bur | st Ac  | dre    | ssing | g (de | cimal) |

|-----------------|--------------------------------|------------------------------------------|------------|---|-------|------|---|---|---|------------|-------|------|-----|--------|--------|-------|-------|--------|

| 0               | xx0                            |                                          |            |   | 0,    | 1    |   |   |   | 0, 1       |       |      |     |        |        |       |       |        |

| 2               | xx1                            |                                          |            |   | 1,    | 0    |   |   |   |            |       |      |     | 1,     | 0      |       |       |        |

|                 | x00                            |                                          |            |   | 0, 1, | 2, 3 |   |   |   |            |       |      |     | 0, 1,  | 2, 3   |       |       |        |

| 4               | x01                            | 1, 2, 3, 0                               |            |   |       |      |   |   |   |            |       |      |     | 1, 0,  | 3, 2   |       |       |        |

| 4               | x10                            |                                          |            |   | 2, 3, | 0, 1 |   |   |   | 2, 3, 0, 1 |       |      |     |        |        |       |       |        |

|                 | x11                            |                                          | 3, 0, 1, 2 |   |       |      |   |   |   | 3, 2, 1, 0 |       |      |     |        |        |       |       |        |

|                 | 000                            | 0                                        | 1          | 2 | 3     | 4    | 5 | 6 | 7 |            | 0     | 1    | 2   | 3      | 4      | 5     | 6     | 7      |

|                 | 001                            | 1                                        | 2          | 3 | 4     | 5    | 6 | 7 | 0 |            | 1     | 0    | 3   | 2      | 5      | 4     | 7     | 6      |

|                 | 010                            | 2                                        | 3          | 4 | 5     | 6    | 7 | 0 | 1 |            | 2     | 3    | 0   | 1      | 6      | 7     | 4     | 5      |

| 8               | 011                            | 3                                        | 4          | 5 | 6     | 7    | 0 | 1 | 2 |            | 3     | 2    | 1   | 0      | 7      | 6     | 5     | 4      |

| 0               | 100                            | 4                                        | 5          | 6 | 7     | 0    | 1 | 2 | 3 |            | 4     | 5    | 6   | 7      | 0      | 1     | 2     | 3      |

|                 | 101                            | 5                                        | 6          | 7 | 0     | 1    | 2 | 3 | 4 |            | 5     | 4    | 7   | 6      | 1      | 0     | 3     | 2      |

|                 | 110                            | 6                                        | 7          | 0 | 1     | 2    | 3 | 4 | 5 |            | 6     | 7    | 4   | 5      | 2      | 3     | 0     | 1      |

|                 | 111                            | 7                                        | 0          | 1 | 2     | 3    | 4 | 5 | 6 |            | 7     | 6    | 5   | 4      | 3      | 2     | 1     | 0      |

| Full Page       | nnn                            | Cn, Cn+1, Cn+2                           |            |   |       |      |   |   |   |            |       |      | n   | ot sup | oporte | ed    |       |        |

## **Refresh Mode**

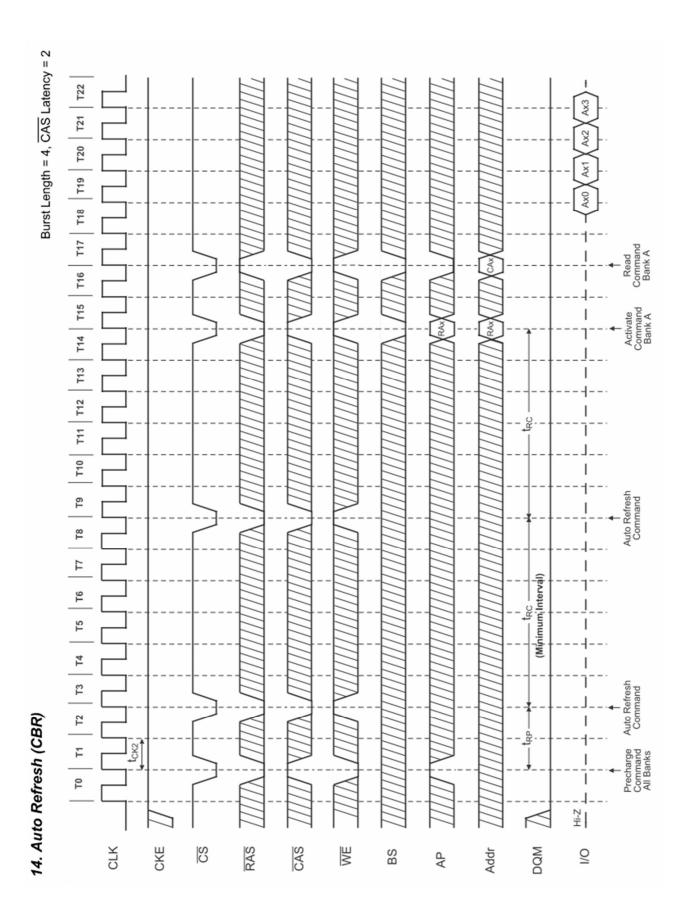

SDRAM has two refresh modes, Auto Refresh and Self Refresh. Auto Refresh is similar to the CAS - before - RAS refresh of conventional DRAMs. All of banks must be precharged before applying any refresh mode. An on-chip address counter increments the word and the bank addresses and no bank information is required for both refresh modes.

The chip enters the Auto Refresh mode, when  $\overline{RAS}$  and  $\overline{CAS}$  are held low and CKE and  $\overline{WE}$  are held high at a clock timing. The mode restores word line after the refresh and no external precharge command is necessary. A minimum  $t_{RC}$  time is required between two automatic refreshes in a burst refresh mode. The same rule applies to any access command after the automatic refresh operation.

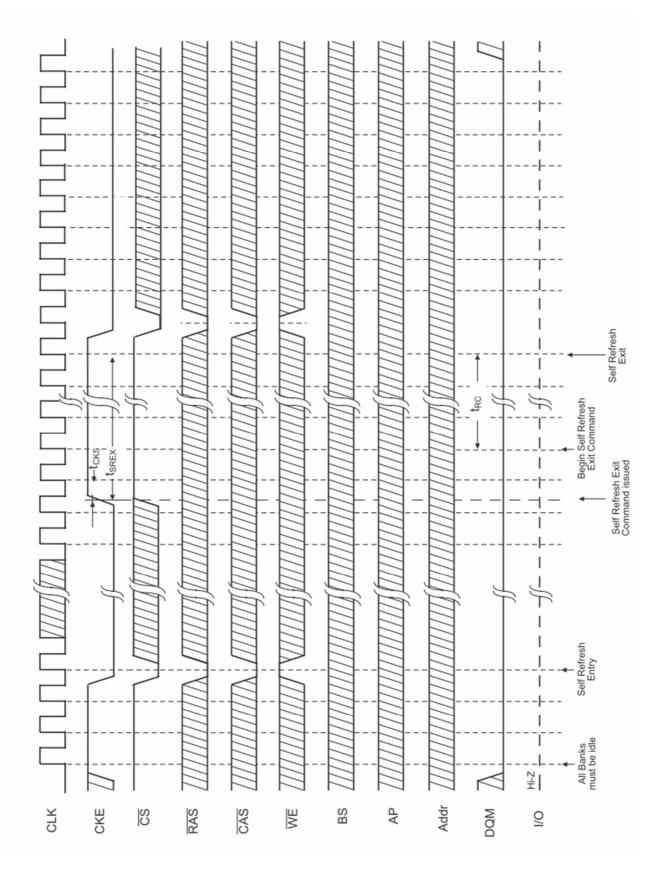

The chip has an on-chip timer and the Self Refresh mode is available. It enters the mode when  $\overline{RAS}$ ,  $\overline{CAS}$ , and CKE are low and  $\overline{WE}$  is high at a clock timing. All of external control signals including the clock are dis- abled. Returning CKE to high enables the clock and initiates the refresh exit operation. After the exit command, at least one  $t_{RC}$  delay is required prior to any access command.

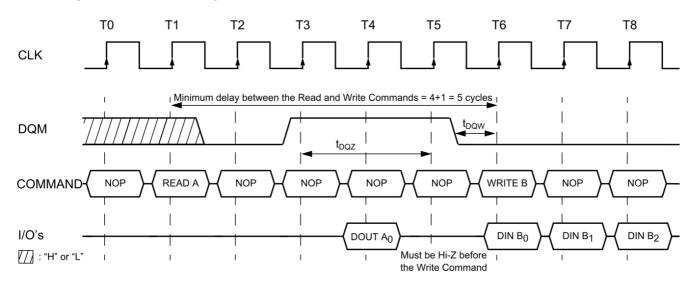

## **DQM** Function

DQM has two functions for data I/O read and write operations. During reads, when it turns to "high" at a clock timing, data outputs are disabled and become high impedance after two clock delay (DQM Data Disable Latency t<sub>DQZ</sub>). It also provides a data mask function for writes. When DQM is activated, the write operation at the next clock is prohibited (DQM Write Mask Latency t<sub>DQW</sub> = zero clocks).

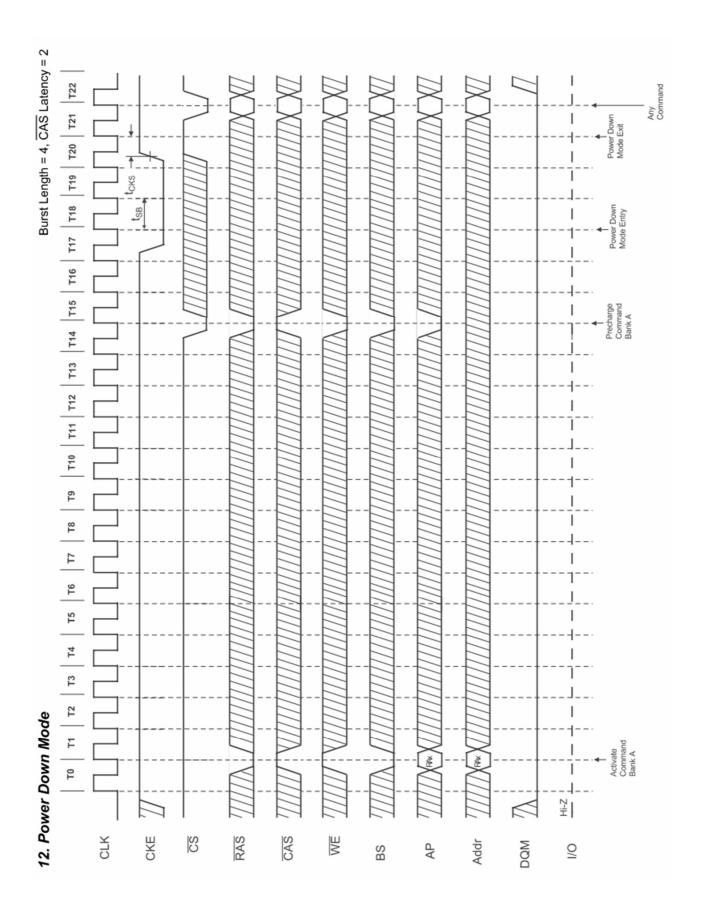

## Power Down

In order to reduce standby power consumption, a power down mode is available. All banks must be precharged and the necessary Precharge delay ( $t_{RP}$ ) must occur before the SDRAM can enter the Power Down mode. Once the Power Down mode is initiated by holding CKE low, all of the receiver circuits except CLK and CKE are gated off. The Power Down mode does not perform any refresh operations, therefore the device can't remain in Power Down mode longer than the Refresh period ( $t_{REF}$ ) of the device. Exit from this mode is performed by taking CKE "high". One clock delay is required for mode entry and exit.

## Auto Precharge

DATASHEFT

Two methods are available to precharge SDRAMs. In an automatic precharge mode, the  $\overline{CAS}$  timing accepts one extra address, CA10, to determine whether the chip restores or not after the operation. If CA10 is high when a Read Command is issued, the **Read with Auto-Precharge** function is initiated. The SDRAM automatically enters the precharge operation one clock before the last data out for  $\overline{CAS}$  latencies 2, two clocks for  $\overline{CAS}$  latencies 3 and three clocks for  $\overline{CAS}$  latencies 4. If CA10 is high when a Write Command is issued, the **Write with Auto-Precharge** function is initiated. The SDRAM automatically enters the precharge operation a time delay equal to t<sub>WR</sub> (Write recovery time) after the last data in. **Auto-Precharge** does not apply to full-page burst mode.

## Precharge Command

There is also a separate precharge command available. When  $\overrightarrow{RAS}$  and  $\overrightarrow{WE}$  are low and  $\overrightarrow{CAS}$  is high at a clock timing, it triggers the precharge operation. Three address bits, BA0, BA1 and A10 are used to define banks as shown in the following list. The precharge command can be imposed one clock before the last data out for  $\overrightarrow{CAS}$  latency = 2, two clocks before the last data out for  $\overrightarrow{CAS}$  latency = 3. Writes require a time delay twr from the last data out to apply the precharge command. A full-page burst may be truncated with a Precharge command to the same bank.

| A10 | BA0 | BA1 |           |

|-----|-----|-----|-----------|

| 0   | 0   | 0   | Bank 0    |

| 0   | 0   | 1   | Bank 1    |

| 0   | 1   | 0   | Bank 2    |

| 0   | 1   | 1   | Bank 3    |

| 1   | Х   | Х   | All Banks |

#### Bank Selection by Address Bits:

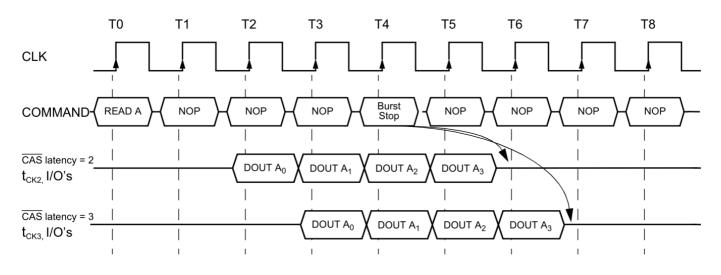

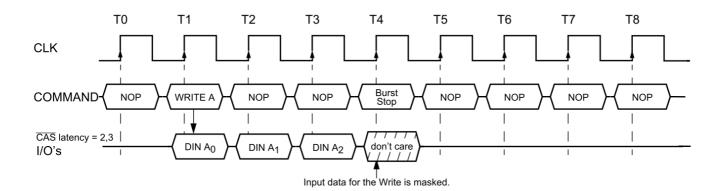

#### **Burst Termination**

Once a burst read or write operation has been initiated, there are several methods in which to terminate the burst operation prematurely. These methods include using another Read or Write Command to interrupt an existing burst operation, use a Precharge Command to interrupt a burst cycle and close the active bank, or using the Burst Stop Command to terminate the existing burst operation but leave the bank open for future Read or Write Commands to the same page of the active bank. When interrupting a burst with another Read or Write Command care must be taken to avoid I/O contention. The Burst Stop Command, however, has the fewest restrictions making it the easiest method to use when terminating a burst operation before it has been completed. If a Burst Stop command is issued during a burst write operation, then any residual data from the burst write cycle will be ignored. Data that is presented on the I/O pins before the Burst Stop Command is registered will be written to the memory. The full-page burst is used in conjunction with Burst Terminate Command to generate arbitrary burst lengths.

INTELLIGENT

## DATASHEET UNLIMITED INGENUITY

## **Recommended D.C. Operating Conditions**

$V_{SS} = 0 \text{ V}; V_{DD}, V_{DDQ} = 3.3 \text{ V} \pm 0.3 \text{ V}$

| Devenueter                                                                            | Quanta            | Limit | Values                | l lusit | Nataa |  |

|---------------------------------------------------------------------------------------|-------------------|-------|-----------------------|---------|-------|--|

| Parameter                                                                             | Symbol            | Min.  | Max.                  | Unit    | Notes |  |

| Input high voltage                                                                    | V <sub>IH</sub>   | 2.0   | V <sub>DD</sub> + 0.3 | V       | 1,2   |  |

| Input low voltage                                                                     |                   | -0.3  | 0.8                   | V       | 1,2   |  |

| Output high voltage (I <sub>OUT</sub> = – 4.0 mA)                                     |                   | 2.4   | -                     | V       |       |  |

| Output low voltage (I <sub>OUT</sub> = 4.0 mA)                                        | V <sub>OL</sub>   | -     | 0.4                   | V       |       |  |

| Input leakage current, any input (0 V < $V_{IN}$ < 3.6 V, all other pins = 0 V)       | I <sub>I(L)</sub> | -2    | 2                     | uA      |       |  |

| Output leakage current<br>(DQ is disabled, 0 V < V <sub>OUT</sub> < V <sub>DD</sub> ) | I <sub>O(L)</sub> | -2    | 2                     | uA      |       |  |

Notes:

1. All voltages are referenced to  $V_{\mbox{\scriptsize SS}}.$

2. V<sub>IH</sub> may overshoot to V<sub>DD</sub> + 2.0 V for pulse width of < 4ns with 3.3V. V<sub>IL</sub> may undershoot to -2.0 V for pulse width < 4.0 ns with 3.3 V. Pulse width measured at 50% points with amplitude measured peak to DC reference.

#### **Operating Currents**

$V_{DD}$  = 3.3 V ± 0.3 V (Recommended Operating Conditions unless otherwise noted)

| Ourseland !       |                                                                                                                                                                                                                  |                                           |     | ax.  |       |     |  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-----|------|-------|-----|--|

| Symbol            | Parameter & Test Condition                                                                                                                                                                                       | -6                                        | -75 | Unit | Notes |     |  |

| I <sub>DD1</sub>  | $\begin{array}{l} \text{Operating Current} \\ t_{\text{RC}} = t_{\text{RC(min)},}, t_{\text{CK}} = t_{\text{CK(min)}} \\ \text{Active-precharge command cycling, without Burst} \\ \text{Operation} \end{array}$ | 1 bank operation                          | 90  | 70   | mA    | 1   |  |

| I <sub>DD2P</sub> | $\label{eq:constraint} \begin{array}{l} \mbox{Precharge Standby Current in Power Down Mode} \\ \hline \hline \hline CS \ = V_{IH}, \ CKE \leq V_{IL(max)} \end{array}$                                           | in Power Down Mode t <sub>ск</sub> = min. |     | 4    | mA    | 1   |  |

| I <sub>DD2N</sub> | $\frac{\text{Precharge Standby Current in Non-Power Down Mode}}{\overline{\text{CS}} = V_{\text{IH}}, \text{CKE} \geq V_{\text{IL}(\text{max})}}$                                                                | t <sub>ск</sub> = min.                    | 15  | 15   | mA    |     |  |

| I <sub>DD3P</sub> | $\overline{CS} = V_{IH(min)}, CKE \le V_{IL(max)}$                                                                                                                                                               | t <sub>ск</sub> = min.                    | 6   | 6    | mA    |     |  |

| I <sub>DD3N</sub> | $\overline{CS} = V_{IH(min)}, CKE \ge V_{IH(min)}$                                                                                                                                                               | t <sub>ск</sub> = min.                    | 20  | 20   | mA    |     |  |

| I <sub>DD4</sub>  | Burst Operating Current Read / Write command cycling                                                                                                                                                             | t <sub>ск</sub> = min.                    | 110 | 90   | mA    | 1,2 |  |

| I <sub>DD5</sub>  | $t_{\rm RC} = t_{\rm RC(min)}$                                                                                                                                                                                   | t <sub>ск</sub> = min.                    | 150 | 120  | mA    | 1   |  |

| I <sub>DD6</sub>  | Self Refresh Current<br>Self Refresh Mode, CKE ≤ 0.2 V                                                                                                                                                           |                                           | 5   | 5    | mA    |     |  |

Notes:

1. These parameters depend on the cycle rate and these values are measured by the cycle rate under the minimum value of t<sub>CK</sub> and t<sub>RC</sub>. Input signals are changed one time during t<sub>CK</sub>.

2. These parameters depend on output loading. Specified values are obtained with output open.

## AC Characteristics

$V_{SS}$  = 0 V;  $V_{DD}$  = 3.3 V ± 0.3 V

| # Symbol |                  |                                                                                                                         |         | Limit Values |           |            |      |       |

|----------|------------------|-------------------------------------------------------------------------------------------------------------------------|---------|--------------|-----------|------------|------|-------|

|          | Symbol           | Parameter                                                                                                               | -6      |              | -75       |            | Unit | Notes |

|          |                  | Min.                                                                                                                    | Max.    | Min.         | Max.      |            |      |       |

| 1        | t <sub>cĸ</sub>  | $\frac{\text{Clock Cycle Time}}{\overline{\text{CAS}} \text{ Latency = 3}}$ $\overline{\text{CAS}} \text{ Latency = 2}$ | 6<br>10 | -            | 7.5<br>10 | -          | ns   |       |

| 2        | t <sub>ск</sub>  | Clock Frequency<br>CAS Latency = 3<br>CAS Latency = 2                                                                   | -       | 166<br>100   | -         | 133<br>100 | MHz  |       |

| 3        | t <sub>AC</sub>  | Access Time from Clock<br>$\overline{CAS}$ Latency = 3<br>$\overline{CAS}$ Latency = 2                                  | -       | 5.4<br>6.0   | -         | 5.4<br>6.0 | ns   | 2,3   |

| 4        | t <sub>скн</sub> | CLK HIGH Level Width                                                                                                    | 2.5     | -            | 2.5       | -          | ns   |       |

| 5        | t <sub>CKL</sub> | CLK LOW Level Width                                                                                                     | 2.5     | -            | 2.5       | -          | ns   |       |

| 6        | t <sub>он</sub>  | Output Data Hold Time                                                                                                   | 2.7     | -            | 2.7       | -          | ns   | 2     |

| 7        | t <sub>LZ</sub>  | Output LOW Impedance Time                                                                                               | 1       | -            | 1         | -          | ns   |       |

| 8        | t <sub>HZ3</sub> |                                                                                                                         | -       | 5.4          | -         | 5.4        | ns   |       |

| 9        | t <sub>HZ2</sub> | Output HIGH Impedance Time                                                                                              | -       | 6.0          | -         | 6.0        | ns   |       |

| 10       | t <sub>DS</sub>  | Input Data Setup Time                                                                                                   | 1.5     | -            | 1.5       | -          | ns   |       |

| 11       | t <sub>DH</sub>  | Input Data Hold Time                                                                                                    | 0.8     | -            | 0.8       | -          | ns   |       |

| 12       | t <sub>AS</sub>  | Address Setup Time                                                                                                      | 1.5     | -            | 1.5       | -          | ns   |       |

| 13       | t <sub>AH</sub>  | Address Hold Time                                                                                                       | 0.8     | -            | 0.8       | -          | ns   |       |

| 14       | t <sub>скs</sub> | CKE Setup Time                                                                                                          | 1.5     | -            | 1,5       | -          | ns   |       |

| 15       | t <sub>скн</sub> | CKE Hold Time                                                                                                           | 0.8     | -            | 0.8       | -          | ns   |       |

| 16       | t <sub>CMS</sub> | Command Setup Time (CS, RAS, CAS, WE, DQM)                                                                              | 1.5     | -            | 1.5       | -          | ns   |       |

| 17       | t <sub>CMH</sub> | Command Hold Time (CS, RAS, CAS, WE, DQM)                                                                               | 0.8     | -            | 0.8       | -          | ns   |       |

| 18       | t <sub>RC</sub>  | Command Period (REF to REF/ACT to ACT)                                                                                  | 60      | -            | 66        | -          | ns   | 5     |

| 19       | t <sub>RAS</sub> | Command Period (ACT to PRE)                                                                                             | 42      | 100K         | 44        | 120K       | ns   | 5     |

| 20       | t <sub>RP</sub>  | Command Period (PRE to ACT)                                                                                             | 15      | -            | 15        | -          | ns   | 5     |

| 21       | t <sub>RCD</sub> | Active Command To Read/Write Command Delay<br>Time                                                                      | 18      | -            | 15        | -          | ns   |       |

| 22       | t <sub>RRD</sub> | Command Period (ACT [0] to ACT[1])                                                                                      | 12      | -            | 15        | -          | ns   | 5     |

| 23       | t <sub>wR</sub>  | Last Data Input to Precharge<br>(Write without Auto Precharge)                                                          | 12      | -            | 15        | -          | ns   |       |

| #  | Symbol           | Parameter                                                                                                                                                                                                                                                                                     | Limit Values |      |      |      |      |       |

|----|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------|------|------|------|-------|

|    |                  |                                                                                                                                                                                                                                                                                               | -6           |      | -75  |      | Unit | Notes |

|    |                  |                                                                                                                                                                                                                                                                                               | Min.         | Max. | Min. | Max. |      |       |

| 24 | t <sub>DAL</sub> | Last Data Input to Precharge<br>(Write with Auto Precharge)                                                                                                                                                                                                                                   | 30           | -    | 30   | -    | ns   |       |

| 25 | t <sub>MRD</sub> | Mode Register Program Time                                                                                                                                                                                                                                                                    | 12           | -    | 15   | -    | ns   |       |

| 26 | t <sub>DDE</sub> | Power Down Exit Setup Time                                                                                                                                                                                                                                                                    | 6            | -    | 7.5  | -    | ns   |       |

| 27 | t <sub>xsR</sub> | Self-Refresh Exit Time                                                                                                                                                                                                                                                                        | 70           | -    | 75   | -    | ns   |       |

| 28 | t⊤               | Transition Time                                                                                                                                                                                                                                                                               | 0.3          | 1.2  | 0.3  | 1.2  | ns   |       |

| 29 | t <sub>REF</sub> | Refresh Cycle Time:<br>Commercial Tambient = 0 to +70°C<br>Industrial Tambient = -40 to +85°C<br>High Temperature Tambient = -40 to +105°C,<br>Tcase(max) = +115°C<br>X-Temp of Extreme Temp. Tambient = -40 to<br>+125°C, Tcase(max) = +135°C<br>Y-Temp of Extreme Temp. Tcase $\leq$ +105°C | -            | 64   | -    | 64   | ms   |       |

|    |                  | Refresh Cycle Time:<br>Y-Temp of Extreme Temp. Tcase > +105°C,<br>Tcase(max) = +135°C                                                                                                                                                                                                         | -            | 32   | -    | 32   | ms   |       |

Notes:

1. For proper power-up see the operation section of this data sheet.

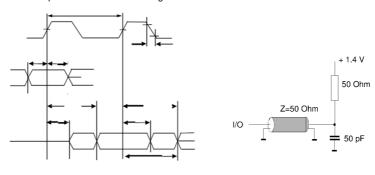

2. AC timing tests have  $V_{IL} = 0.4V$  and  $V_{IH} = 2.4V$  with the timing referenced to the 1.4 V crossover point. The transition time is measured between  $V_{IH}$  and  $V_{IL}$ . All AC measurements assume  $t_T = 1$ ns with the AC output load circuit shown in Figure 1.

Figure 1

3. If clock rising time is longer than 1 ns, a time  $(t_T/2 - 0.5)$  ns has to be added to this parameter.

4. If  $t_T$  is longer than 1 ns, a time  $(t_T \ -1)$  ns has to be added to this parameter.

5. These parameter account for the number of clock cycle and depend on the operating frequency of the clock, as follows:

The number of clock cycle = specified value of timing period (counted in fractions as a whole number)

Self Refresh Exit is a synchronous operation and begins on the  $2^{nd}$  positive clock edge after CKE returns high. Self Refresh Exit is not complete until a time period equal to  $t_{RC}$  is satisfied once the Self Refresh Exit command is registered.

6. Referenced to the time which the output achieves the open circuit condition, not to output voltage levels.

## Timing Diagrams

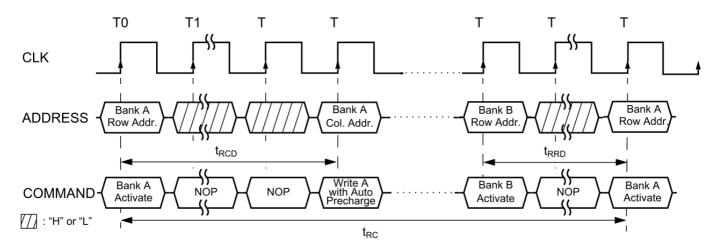

- 1. Bank Activate Command Cycle

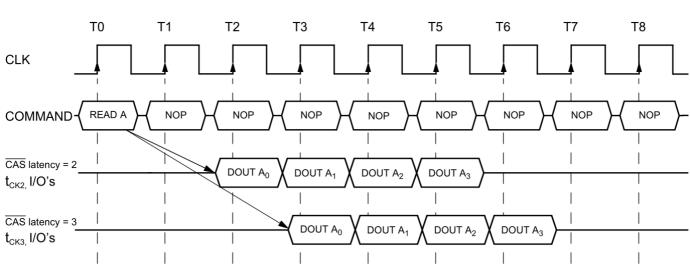

- 2. Burst Read Operation

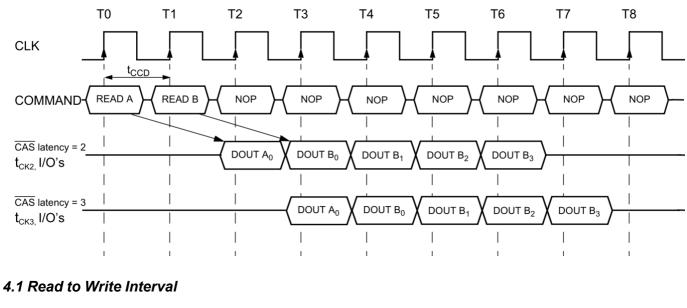

- 3. Read Interrupted by a Read

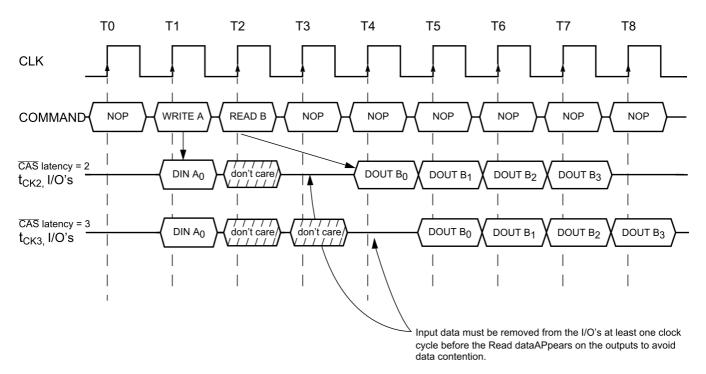

- 4. Read to Write Interval

- 4.1 Read to Write Interval

- 4.2 Minimum Read to Write Interval

- 4.3 Non-Minimum Read to Write Interval

- 5. Burst Write Operation

- 6. Write and Read Interrupt

- 6.1 Write Interrupted by a Write

- 6.2 Write Interrupted by Read

- 7. Burst Write & Read with Auto-Precharge

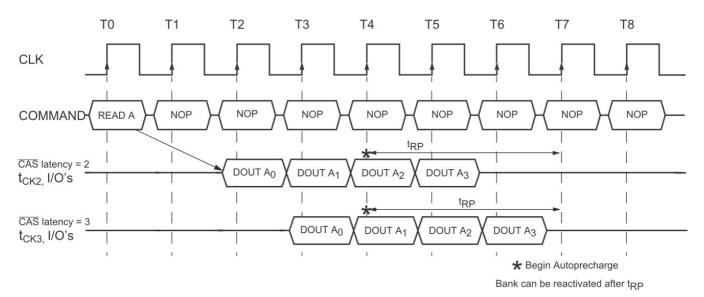

- 7.1 Burst Write with Auto-Precharge7.2 Burst Read with Auto-Precharge

- 8. Burst Termination

- 8.1 Termination of a Burst Write Operation8.2 Termination of a Burst Write Operation

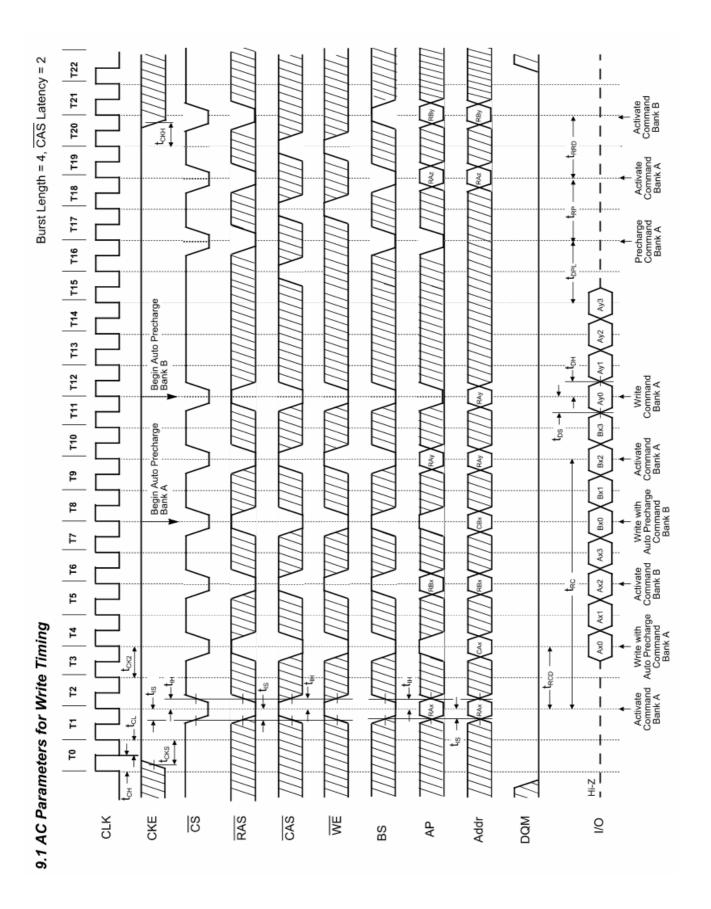

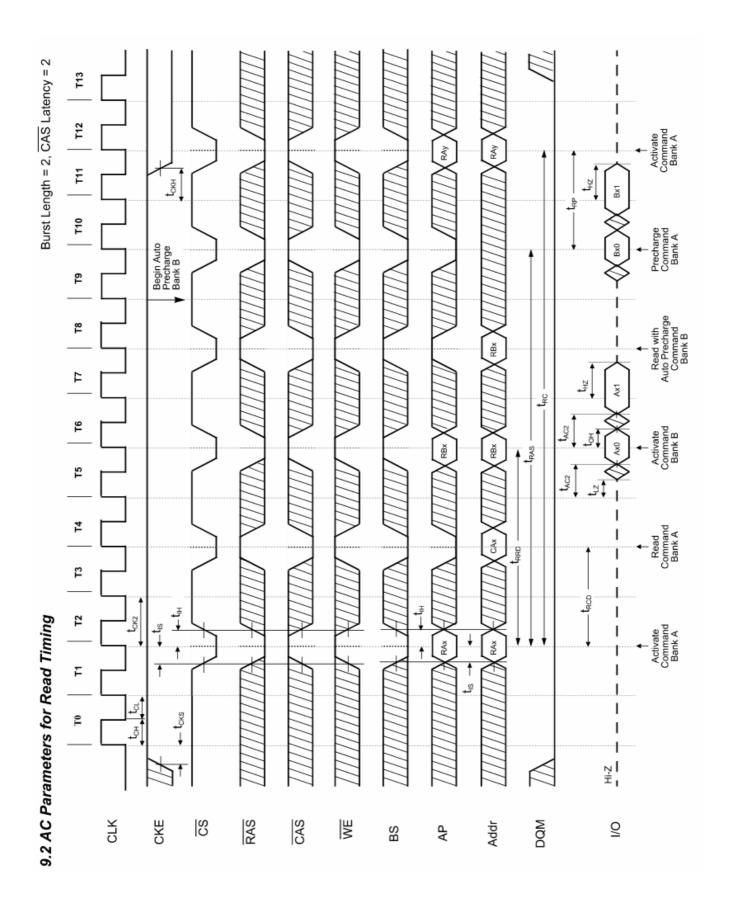

- 9. AC- Parameters

- 9.1 AC Parameters for a Write Timing9.2 AC Parameters for a Read Timing

- 10. Mode Register Set

- 11. Power on Sequence and Auto Refresh (CBR)

- 12. Power Down Mode

- 13. Self Refresh (Entry and Exit)

- 14. Auto Refresh (CBR)

## Timing Diagrams (Cont'd)

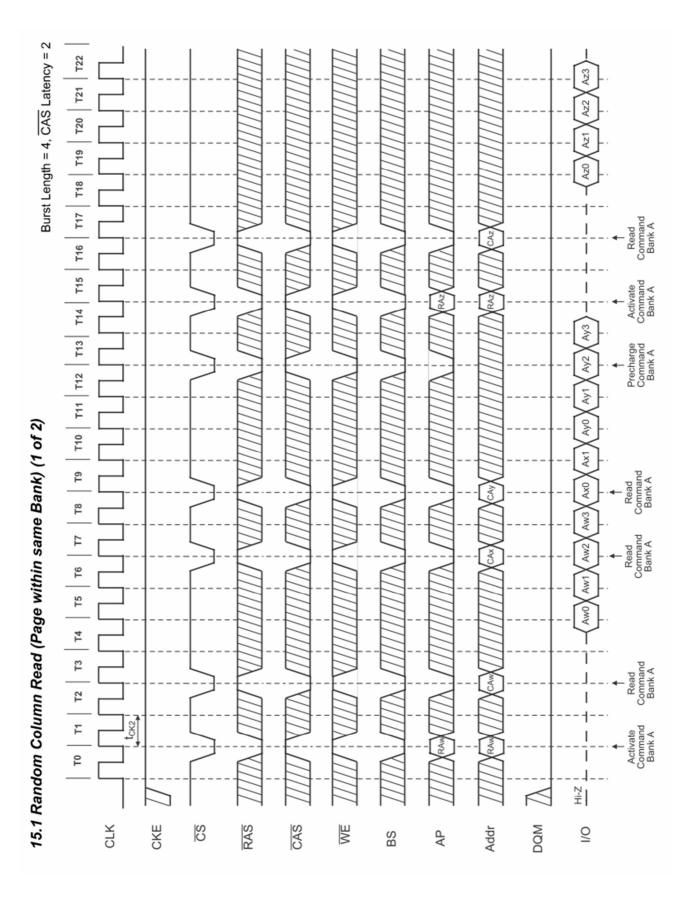

15. Random Column Read (Page within same Bank)

15.1 CAS Latency = 2 15.2 CAS Latency = 3

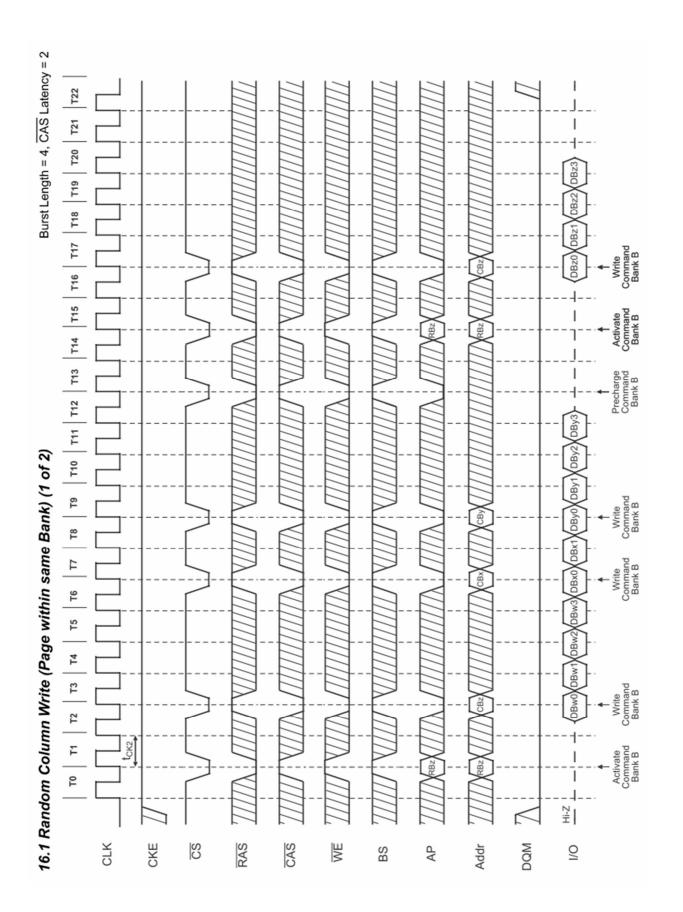

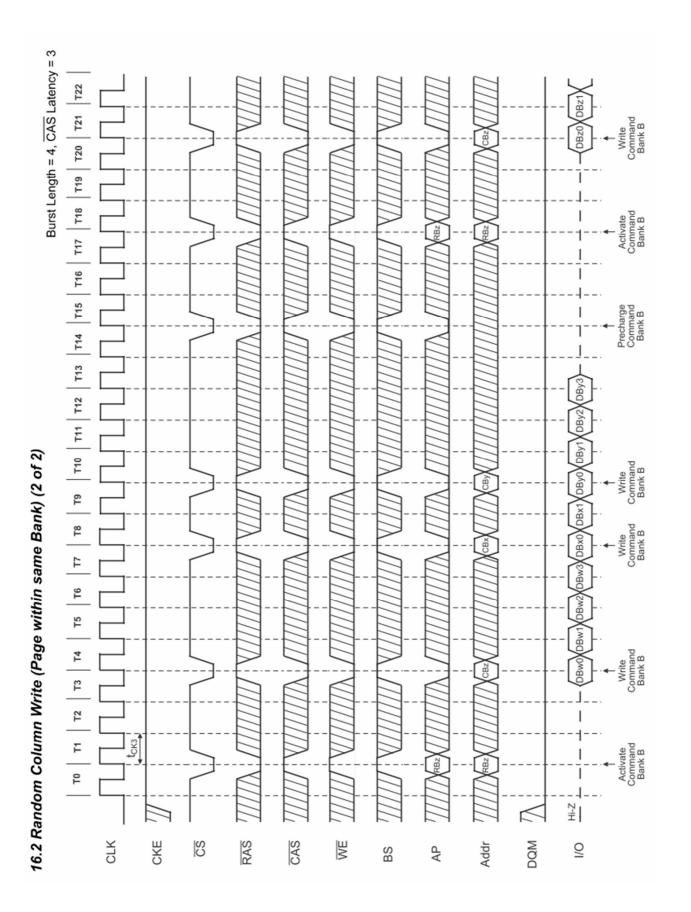

16. Random Column Write (Page within same Bank)

16.1 <u>CAS</u> Latency = 2 16.2 <u>CAS</u> Latency = 3

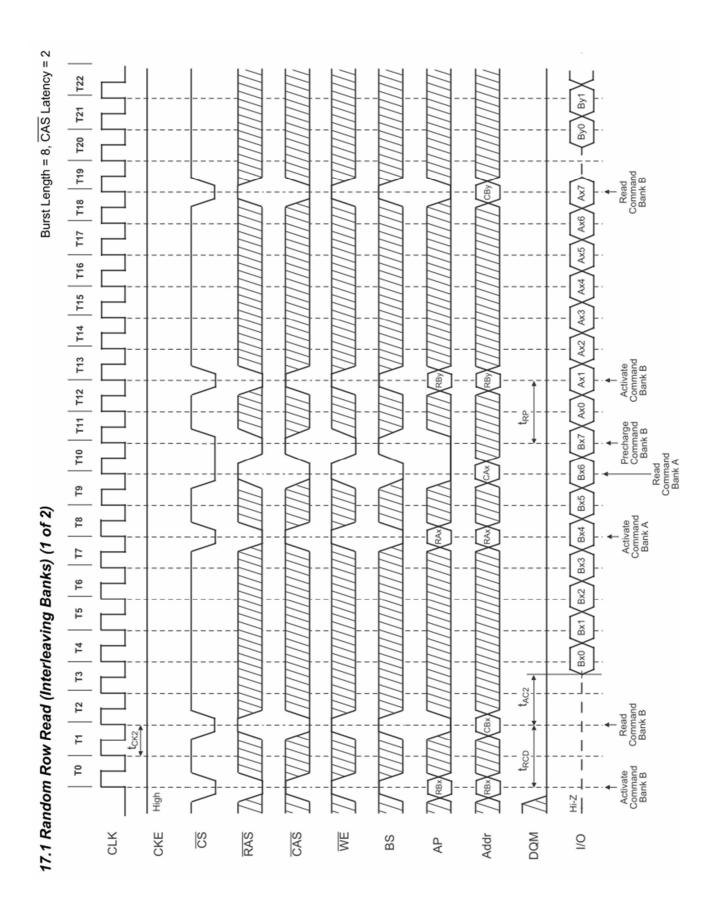

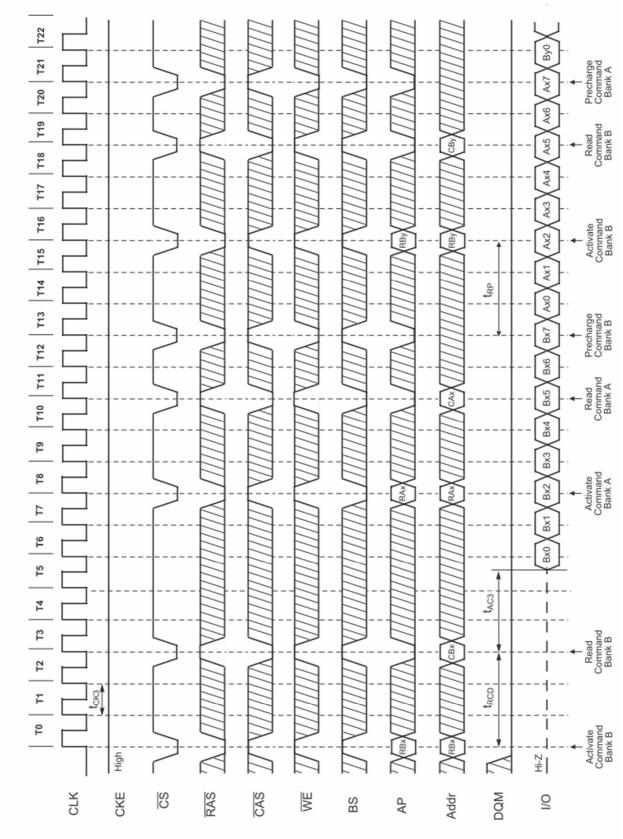

17. Random Row Read (Interleaving Banks) with Precharge

17.1  $\overline{CAS}$  Latency = 2 17.2  $\overline{CAS}$  Latency = 3

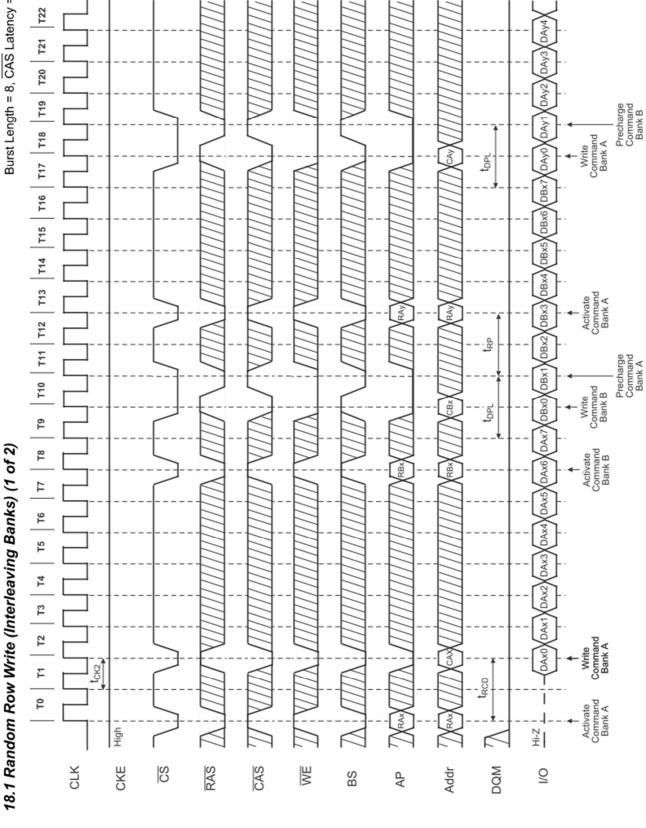

18. Random Row Write (Interleaving Banks) with Precharge

18.1 CAS Latency = 2 18.2 CAS Latency = 3

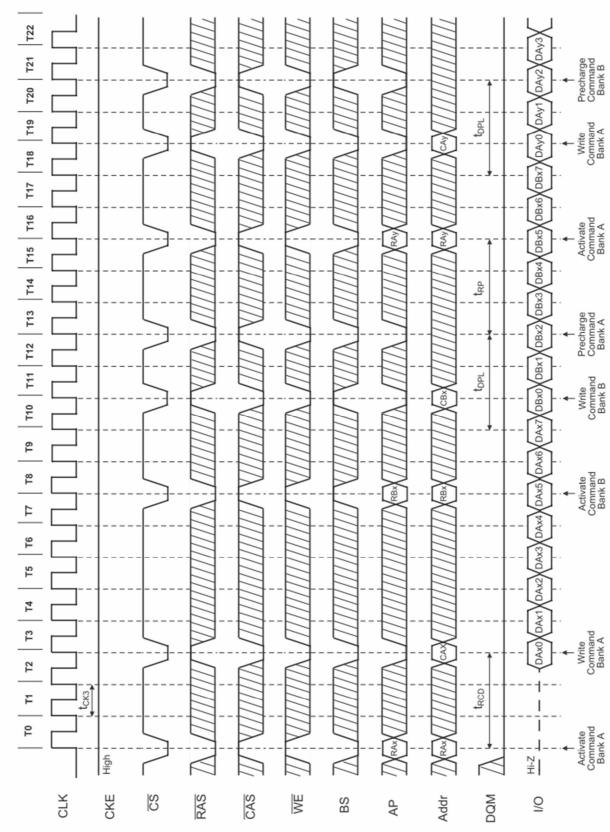

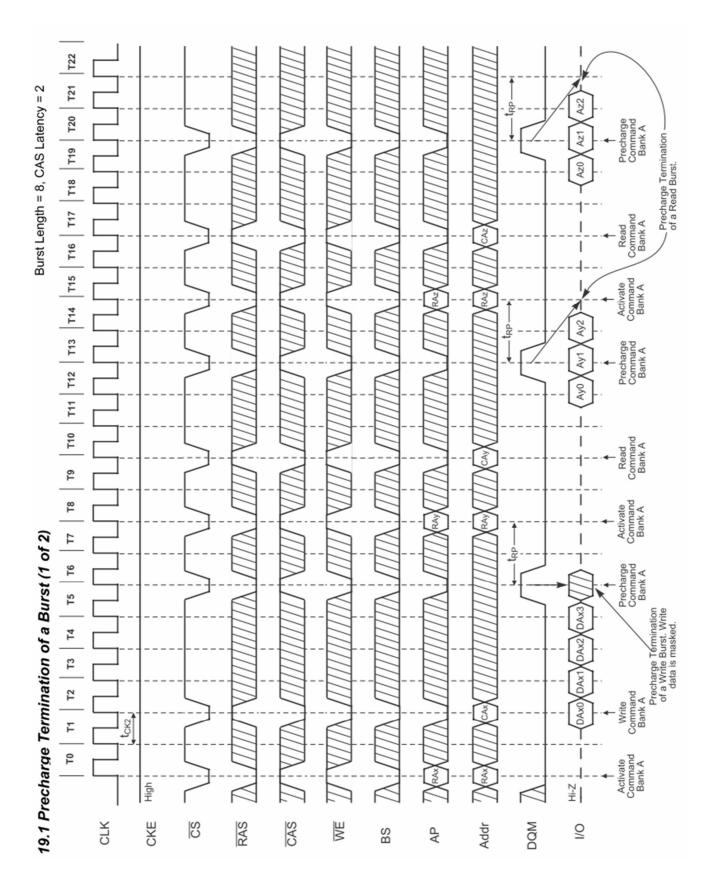

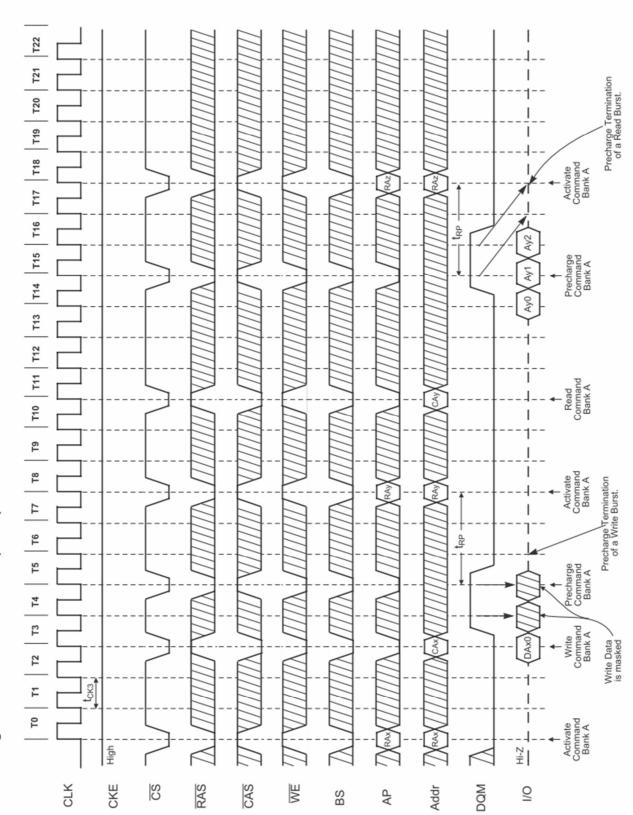

19. Precharge Termination of a Burst

19.1 CAS Latency = 2 19.2 CAS Latency = 3

20. Full Page Burst Operation

20.1 Full Page Burst Read,  $\overline{CAS}$  Latency = 2 20.2 Full Page Burst Read,  $\overline{CAS}$  Latency = 3

21. Full Page Burst Operation

21.1 Full Page Burst Write,  $\overline{CAS}$  Latency = 2 21.2 Full Page Burst Write,  $\overline{CAS}$  Latency = 3

## 1. Bank Activate Command Cycle

## 2. Burst Read Operation

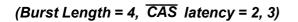

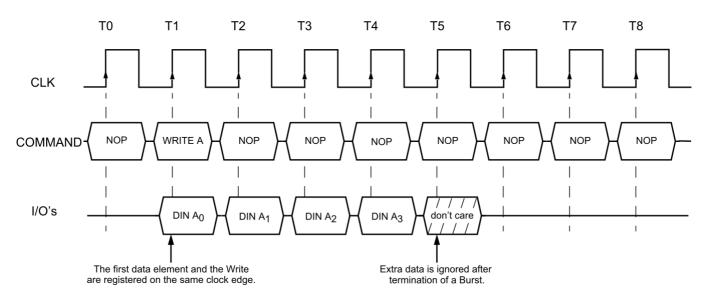

## (Burst Length = 4, $\overline{CAS}$ latency = 2, 3)

## 3. Read Interrupted by a Read

DATASHEET

UNLIMITED INGENUIT

INTELLIGENT

MEMORY

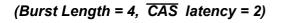

## (Burst Length = 4, $\overline{CAS}$ latency = 3)

## (Burst Length = 4, $\overline{CAS}$ latency = 2, 3)

## DATASHEET UNLIMITED INGENUIT INTELLIGENT

## 4.2 Minimum Read to Write Interval

## 4.3 Non-Minimum Read to Write Interval

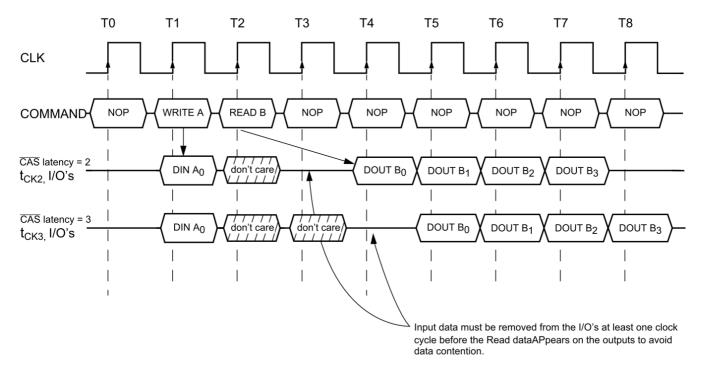

#### (Burst Length = 4, $\overline{CAS}$ latency = 2, 3) Т0 Τ1 Τ2 ТЗ Τ4 Τ5 Т6 CLK t<sub>DQW</sub> DQM t<sub>DQZ</sub> NOP READ A COMMAND READ A NOP NOP NOP

Τ7

Τ8

## 5. Burst Write Operation

DATASHEET

UNI IMITED INGENUIT

INTELLIGENT

MFMORY

#### 6.1 Write Interrupted by a Write

## 6.2 Write Interrupted by a Read

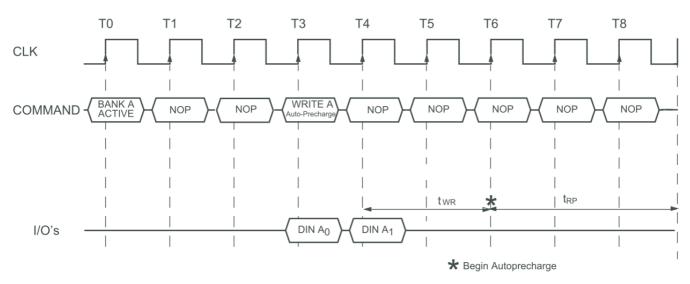

## 7.1 Burst Write with Auto-Precharge

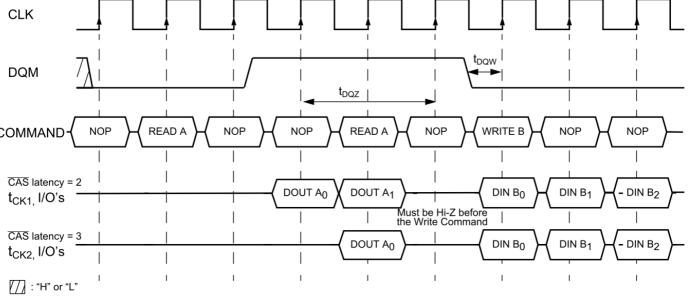

## Burst Length = 2, $\overline{CAS}$ latency = 2, 3)

Bank can be reactivated after trp

## 7.2 Burst Read with Auto-Precharge

## Burst Length = 4, $\overline{CAS}$ latency = 2, 3)

Datasheet Version 3.0

## 8.1 Termination of a Burst Read Operation

## $(\overline{CAS} | atency = 2, 3)$

## 8.2 Termination of a Burst Write Operation

UNLIMITED INGENUITY

INTELLIGENT MEMORY

UNLIMITED INGENUITY

DATASHEET

UNLIMITED INGENUITY INTELLIGENT MEMORY

DATASHEET

UNLIMITED INGENUIT

INTELLIGENT MEMORY

INTELLIGENT MEMORY

UNLIMITED INGENUITY

13. Self Refresh (Entry and Exit)

DATASHEET

UNLIMITED INGENUITY

INTELLIGENT MEMORY

UNLIMITED INGENUITY

DATASHEET

UNLIMITED INGENUIT

INTELLIGENT MEMORY

UNLIMITED INGENUIT

INTELLIGENT MEMORY

35

UNLIMITED INGENUIT

INTELLIGENT MEMORY

DATASHEET

UNLIMITED INGENUIT

INTELLIGENT MEMORY

Burst Length = 8, CAS Latency = 3

DATASHEET

17.2 Random Row Read (Interleaving Banks) (2 of 2)

Burst Length = 8, CAS Latency = 2

DATASHEET

Burst Length = 8, CAS Latency = 3

DATASHEET

18.2 Random Row Write (Interleaving Banks) (2 of 2)

UNLIMITED INGENUIT

INTELLIGENT MEMORY

UNLIMITED INGENUITY INTELLIGENT MEMORY

DATASHEET

Burst Length = 4, 8, CAS Latency = 3

DATASHEET

19.2 Precharge Termination of a Burst (2 of 2)

DATASHEET

20.1 Full Page Read Cycle (1 of 2)

DATASHEET

20.2 Full Page Read Cycle (2 of 2)

DATASHEET

21.1 Full Page Write Cycle (1 of 2)

DATASHEET

21.2 Full Page Write Cycle (2 of 2)

# Complete List of Operation Commands

### SDRAM Function Truth Table

DATASHEET

| CURREN<br>T STATE <sup>1</sup> | CS | RAS | CAS | WE | BS  | Addr  | ACTION                                                   |

|--------------------------------|----|-----|-----|----|-----|-------|----------------------------------------------------------|

|                                | Н  | х   | х   | х  | х   | х     | NOP or Power Down                                        |

|                                | L  | н   | н   | н  | х   | х     | NOP                                                      |

|                                | L  | н   | н   | L  | BS  | х     | ILLEGAL <sup>2</sup>                                     |

|                                | L  | н   | L   | х  | BS  | х     | ILLEGAL <sup>2</sup>                                     |

| Idle                           | L  | L   | н   | н  | BS  | RA    | Row (&Bank) Active; Latch Row Address                    |

|                                | L  | L   | н   | L  | BS  | AP    | NOP4                                                     |

|                                | L  | L   | L   | н  | х   | х     | Auto-Refresh or Self-Refresh <sup>5</sup>                |

|                                | L  | L   | L   | L  | Op- | Code  | Mode reg. Access <sup>5</sup>                            |

|                                | Н  | Х   | Х   | Х  | Х   | х     | NOP                                                      |

|                                | L  | Н   | Н   | Х  | Х   | Х     | NOP                                                      |

|                                | L  | Н   | L   | Н  | BS  | CA,AP | Begin Read; Latch CA; DetermineAP Begin Write; Latch CA; |

| Row Active                     | L  | Н   | L   | L  | BS  | CA,AP | DetermineAP                                              |

|                                | L  | L   | Н   | Н  | BS  | Х     | ILLEGAL <sup>2</sup>                                     |

|                                | L  | L   | Н   | L  | BS  | AP    | Precharge                                                |

|                                | L  | L   | L   | Х  | Х   | х     | ILLEGAL                                                  |

|                                | Н  | х   | х   | Х  | х   | х     | NOP (Continue Burst to End;>Row Active)                  |

|                                | L  | н   | н   | н  | Х   | Х     | NOP (Continue Burst to End;>Row Active)                  |

|                                | L  | н   | н   | L  | BS  | Х     | Burst Stop Command > Row Active                          |

| Dood                           | L  | н   | L   | н  | BS  | CA,AP | Term Burst, New Read, DetermineAP <sup>3</sup>           |

| Read                           | L  | н   | L   | L  | BS  | CA,AP | Term Burst, Start Write, DetermineAP <sup>3</sup>        |

|                                | L  | L   | н   | н  | BS  | Х     | ILLEGAL <sup>2</sup>                                     |

|                                | L  | L   | Н   | L  | BS  | AP    | Term Burst, Precharge                                    |

|                                | L  | L   | L   | Х  | Х   | х     | ILLEGAL                                                  |

|                                | Н  | х   | х   | х  | х   | х     | NOP (Continue Burst to End;>Row Active)                  |

|                                | L  | н   | н   | н  | Х   | Х     | NOP (Continue Burst to End;>Row Active)                  |

|                                | L  | н   | н   | L  | BS  | Х     | Burst Stop Command > Row Active                          |

| Write                          | L  | Н   | L   | Н  | BS  | CA,AP | Term Burst, Start Read, DetermineAP <sup>3</sup>         |

| vvnie                          | L  | Н   | L   | L  | BS  | CA,AP | Term Burst, New Write, DetermineAP <sup>3</sup>          |

|                                | L  | L   | Н   | Н  | BS  | Х     | ILLEGAL <sup>2</sup>                                     |

|                                | L  | L   | Н   | L  | BS  | AP    | Term Burst, Precharge <sup>3</sup>                       |

|                                | L  | L   | L   | Х  | Х   | Х     | ILLEGAL                                                  |

|                                | Н  | х   | х   | х  | х   | х     | NOP (Continue Burst to End;> Precharge)                  |

|                                | L  | н   | н   | Н  | Х   | Х     | NOP (Continue Burst to End;> Precharge)                  |

| Read with                      | L  | н   | н   | L  | BS  | Х     | ILLEGAL <sup>2</sup>                                     |

|                                | L  | Н   | L   | Н  | BS  | х     | ILLEGAL <sup>2</sup>                                     |

| Auto<br>Precharge              | L  | Н   | L   | L  | х   | х     | ILLEGAL                                                  |

| Precharge                      | L  | L   | Н   | Н  | BS  | х     | ILLEGAL <sup>2</sup>                                     |

|                                | L  | L   | Н   | L  | BS  | AP    | ILLEGAL <sup>2</sup>                                     |

|                                | L  | L   | L   | Х  | х   | х     | ILLEGAL                                                  |

## SDRAM Function Truth Table (continued)

DATASHEET

| T STATE <sup>1</sup> | CS | RAS    | CAS | WE | BS      | Addr | ACTION                                  |

|----------------------|----|--------|-----|----|---------|------|-----------------------------------------|

|                      | н  | х      | х   | х  | х       | х    | NOP (Continue Burst to End;> Precharge) |

|                      | L  | н      | н   | н  | х       | х    | NOP (Continue Burst to End;> Precharge) |

|                      | L  | н      | н   | L  | BS      | х    | ILLEGAL <sup>2</sup>                    |

| Write with           | L  | н      | L   | н  | BS      | х    | ILLEGAL <sup>2</sup>                    |

| Auto                 | L  | н      | L   | L  | х       | х    | ILLEGAL                                 |

| Precharge            | L  | L      | н   | н  | BS      | х    | ILLEGAL <sup>2</sup>                    |

|                      | L  | L      | н   | L  | BS      | AP   | ILLEGAL <sup>2</sup>                    |

|                      | L  | L      | L   | Х  | Х       | х    | ILLEGAL                                 |

|                      | Н  | х      | Х   | Х  | Х       | х    | NOP;> Idle after tRP                    |

|                      | L  | н      | н   | н  | Х       | х    | NOP;> Idle after Trp                    |

|                      | L  | н      | н   | L  | BS      | х    | ILLEGAL <sup>2</sup>                    |

| Precharging          | L  | н      | L   | х  | BS      | х    | ILLEGAL <sup>2</sup>                    |